A/D converter

12_BIT_DAC_WITH_VARIABLE_STEP_SIZE

Published:2009/7/1 21:31:00 Author:May | From:SeekIC

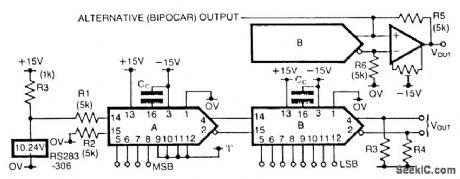

The step size of the converter is variable by selection of the high order data bits.The first DAC, A, has a stable reference current supplied via the 10.24 V reference IC and R1. R2 provides bias cancellation. As shown, only the first 4 MSB inputs are used, giving a step size of225/256 x 2.048/16 = 0.127 mA. This current supplies the reference for DAC B whose step size is then 0.1275/256 = 0.498 μA. Complementary voltage outputs are available for unipolar output and using R3 = R4 = 10 K, Vout is ±10.2 V pproximately, with a step size (1 LSB) of approximately 5 mV. If desired an op amp can be added to the output to provide a low impedance output with bipolar output symmetrical about ground, if R5 = R6 within 0.05%. Note that offset null is required, and all resistors except R2 and R3 should be 1% high stability types.By using lower order address lines than illustrated for DAC A, a smaller step size (and therefore full-scale output) can be obtained. Unused high order bits can be manipulated high or low to change the relative position of the full-scale output.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/A-D_D-A_Converter_Circuit/A-D_converter/12_BIT_DAC_WITH_VARIABLE_STEP_SIZE.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: