Position: Home > Circuit Diagram > Measuring and Test Circuit > The level test circuit with CMOS NAND gate 4011 connected into inverter

Measuring and Test Circuit

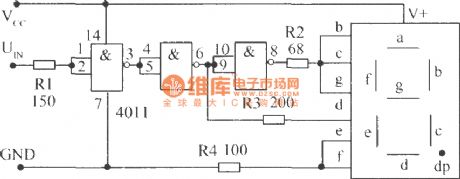

The level test circuit with CMOS NAND gate 4011 connected into inverter

Published:2012/9/16 22:53:00 Author:Ecco | Keyword: level test , CMOS NAND gate , inverter | From:SeekIC

In this circuit, it can also use NOT gate to replace 4011. High level displays H, low level displays L. R2 ~ R4 play a limiting role, so the digital tube and its anode are connected to the positive power supply Vcc directly. The normally on segments e , f are grounded by R4 to reduce the drive current.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Measuring_and_Test_Circuit/The_level_test_circuit_with_CMOS_NAND_gate_4011_connected_into_inverter.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: