Features: • 16 x 16 parallel multiplier-accumulator with selectable accumulation and subtraction

• High-speed: 20ns multiply-accumulate time

• IDT7210 features selectable accumulation, subtraction, rounding and preloading with 35-bit result

• IDT7210 is pin and function compatible with the TRW TDC1010J, TMC2210, Cypress CY7C510, and AMD AM29510

• Performs subtraction and double precision addition and multiplication

• Produced using advanced CMOS high-performance technology

• TTL-compatible

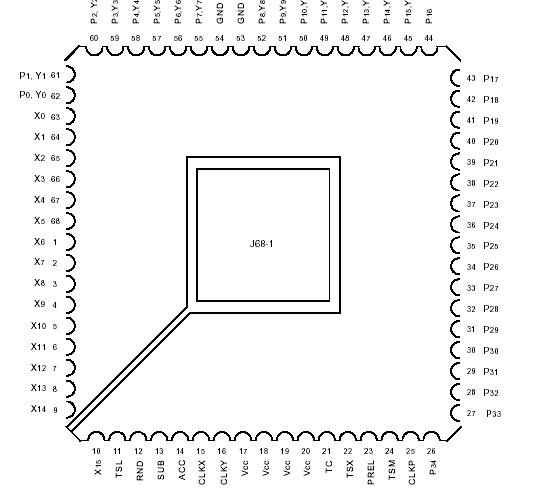

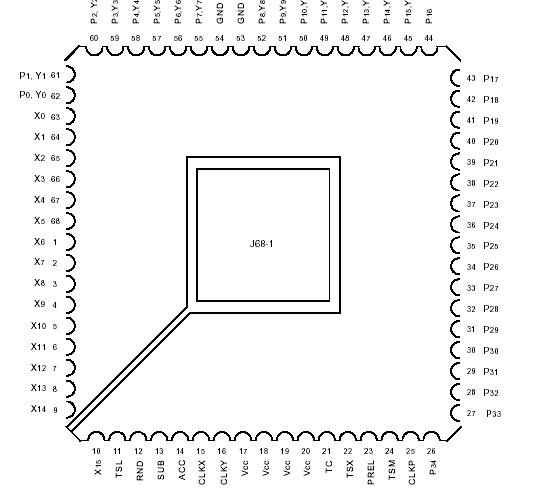

• Available in PLCC

• Speeds available: L20/25/35Pinout Specifications

Specifications

|

Symbol |

Description |

Max

|

Unit |

|

VTERM |

Power Supply Voltage |

0.5 to +7 |

V |

|

VTERM |

Terminal Voltage with Respect to GND |

0.5 to VCC + 0.5 |

V |

|

VTER(2) |

Operating Temperature |

0.5 to +7 |

v |

|

TSTG |

Storage Temperature |

55 to +125

|

°C |

|

IOUT |

DC Output Current |

50

|

mA |

NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

DescriptionThe IDT7210 is a high-speed, low-power 16 x 16-bit parallel multiplieraccumulator that is ideally suited for real-time digital signal processing applications. Fabricated using CMOS silicon gate technology, this IDT7210 offers a very low-power alternative to existing bipolar and NMOS counterparts, with only 1/7 to 1/10 the power dissipation and exceptional speed (25ns maximum) performance.

A pin and functional replacement for TRW's TDC1010J, the IDT7210 operates from a single 5 volt supply and is compatible with standard TTL logic levels. The architecture of the IDT7210 is fairly straightforward,featuring individual input and output registers with clocked D-type flip-flop, a preload capability which enables input data to be preloaded into the output registers, individual three-state output ports for the Extended Product (XTP) and Most Significant Product (MSP) and a Least Significant Product output (LSP) which is multiplexed with the Y input.

The XIN and YIN data input registers may be specified through the use of the Two's Complement input (TC) as either a two's complement or an unsigned magnitude, yielding a full-precision 32-bit result that may be accumulated to a full 35-bit result. The three output registers Extended Product (XTP), Most Most Significant Product (MSP) and Least Significant Product (LSP) are controlled by the respective TSX, TSM and TSL input lines.

The LSP output can be routed through YIN ports. Accumulate input (ACC) enables the device to perform either a multiply or a multiply-accumulate function. In the multiply-accumulate mode, output data can be added to or subtracted from previous results. When the Subtraction (SUB) input is active simultaneously with an active ACC, a subtraction can be performed.

The double precision accumulated result is rounded down to either a single precision or single precision plus 3-bit extended result. In the multiply mode, the Extended Product output (XTP) is sign extended in the two's complement mode or set to zero in the unsigned mode.

The Round (RND) control rounds up the Most Significant Product (MSP) and the 3-bit Extended Product (XTP) outputs. When Preload input (PREL) is active, all the output buffers are forced into a high-impedance state (see Preload truth table) and external data can be loaded into the output register by using the TSX, TSL and TSM signals as input controls.p;

40962 Data Sheet

40962 Data Sheet