Features: •Std., A, and C speed grades

•Low input and output leakage £1mA (max.)

•CMOS power levels

•True TTL input and output compatibility VOH = 3.3V (typ.) VOL = 0.3V (typ.)

•High drive outputs (-15mA IOH, 48mA IOL)

•Meets or exceeds JEDEC standard 18 specifications

•Product available in Radiation Tolerant and Radiation Enhanced versions

•Military product compliant to MIL-STD-883, Class B and DESC listed (dual marked)

•Available in DIP, SOIC, QSOP, CERPACK and LCC packages

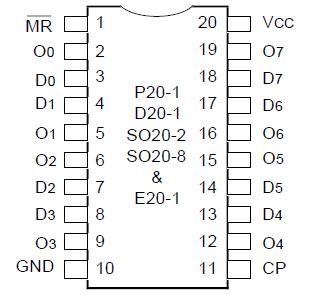

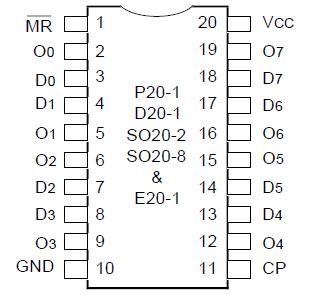

Pinout Specifications

Specifications

| Symbol |

Rating |

Commercial |

Military |

Unit |

| VTERM(2) |

Terminal Voltage

with Respect to

GND |

0.5 to +7.0 |

0.5 to +7.0 |

V |

| VTERM(3) |

Terminal Voltage

with Respect to

GND |

0.5 to

VCC +0.5 |

0.5 to

VCC +0.5 |

V |

| TA |

Operating

Temperature |

0 to +70 |

55 to +125 |

|

| TBIAS |

Temperature

Under Bias |

55 to +125 |

65 to +135 |

|

| TSTG |

Storage

Temperature |

55 to +125 |

65 to +150 |

|

| PT |

Power Dissipation |

0.5 |

0.5 |

W |

| IOUT |

DC Output

Current |

60 to +120 |

60 to +120 |

mA |

DescriptionThe 74FCT273T is octal D flip-flops built using an advanced dual metal CMOS technology. The 74FCT273T has eight edge-triggered D-type flipflops with individual D inputs and O outputs. The common buffered Clock (CP) and Master Reset (MR ) inputs load and reset (clear) all flip-flops simultaneously.

The register of the 74FCT273T is fully edge-triggered. The state of each D input, one set-up time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop's O output.

All outputs of the 74FCT273T will be forced LOW independently of Clock or Data inputs by a LOW voltage level on the MR input. The device is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.

74FCT273T Data Sheet

74FCT273T Data Sheet