Features: Receive path includes dual 10-bit analog-to-digital converters with internal or external reference, 50 MSPS and 80 MSPS versions

Transmit path includes dual 10-bit, 200 MSPS digital-to-analog converters with 1*, 2*, or 4* interpolation and programmable gain control

Internal clock distribution block includes a programmable phase-locked loop and timing generation circuitry, allowing single-reference clock operation

20-pin flexible I/O data interface allows various interleaved or noninterleaved data transfers in half-duplex mode and interleaved data transfers in full-duplex mode

Configurable through register programmability or optionally limited programmability through mode pins

Independent Rx and Tx power-down control pins

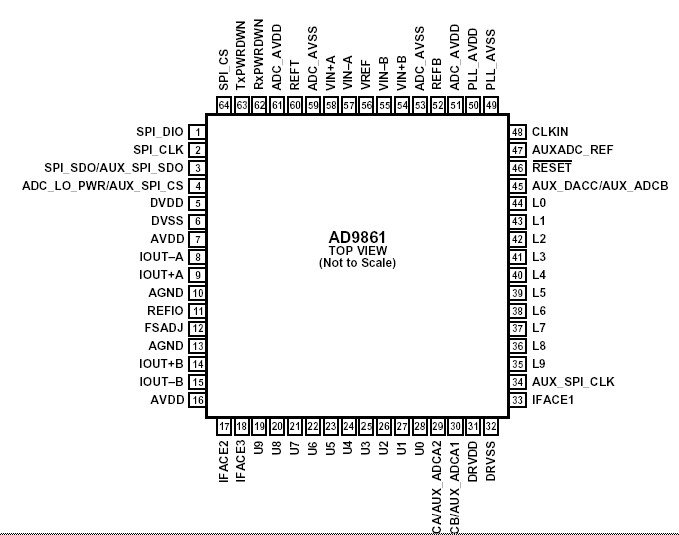

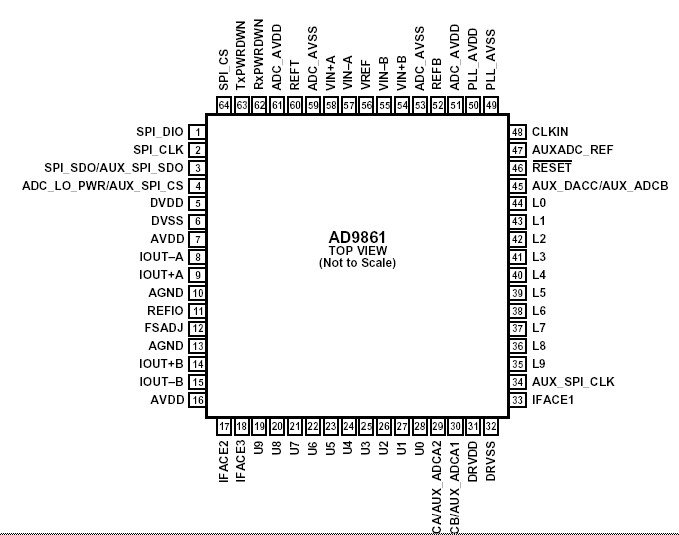

64-lead LFCSP package (9 mm * 9 mm footprint)

3 configurable auxiliary converter pins

ApplicationBroadband access

Broadband LAN

Communications (modems)Pinout

Specifications

Specifications

| Parameter |

Rating |

Electrical

AVDD Voltage

DRVDD Voltage

Analog Input Voltage

Digital Input Voltage

Digital Output Current |

3.9 V max

3.9 V max

−0.3 V to AVDD + 0.3 V

−0.3 V to DVDD − 0.3 V

5 mA max |

Environmental

Operating Temperature Range

(Ambient)

Maximum Junction Temperature

Lead Temperature

(Soldering, 10 sec)

Storage Temperature Range

(Ambient) |

−40°C to +85°C

150°C

300°C

−65°C to +150°C |

| Resolution (Bits) |

10bit |

| T-Put Rate |

80MSPS |

| # Chan |

2 |

| Supply V |

Single(+3),Single(+3.3) |

| Interface |

Par |

| Ain Range |

2 V p-p |

| SNR (dB) |

60dB |

| Pkg Type |

CSP |

DescriptionThe AD9861 is a member of the MxFE family-a group of integrated converters for the communications market. The AD9861 integrates dual 10-bit analog-to-digital converters (ADC) and dual 10-bit digital-to-analog converters (TxDAC®). Two speed grades are available, -50 and -80. The -50 is opti-mized for ADC sampling of 50 MSPS and less, while the -80 is optimized for ADC sample rates between 50 MSPS and 80 MSPS. The dual TxDACs operate at speeds up to 200 MHz and include a bypassable 2* or 4* interpolation filter. Three auxiliary converters are also available to provide required system level control voltages or to monitor system signals. The AD9861 is optimized for high performance, low power, small form factor, and to provide a cost-effective solution for the broadband communication market.

The AD9861 uses a single input clock pin (CLKIN) to generate all system clocks. The ADC and TxDAC clocks are generated within a timing generation block that provides user programma-ble options such as divide circuits, PLL multipliers, and switches.

A flexible, bidirectional 20-bit I/O bus accommodates a variety of custom digital back ends or open market DSPs.

In half-duplex systems, the interface supports 20-bit parallel transfers or 10-bit interleaved transfers. In full-duplex systems, the interface supports an interleaved 10-bit ADC bus and an interleaved 10-bit TxDAC bus. The flexible I/O bus reduces pin count and, therefore, reduces the required package size on the AD9861 and the device to which it connects.

The AD9861 can use either mode pins or a serial program-mable interface (SPI) to configure the interface bus, operate the ADC in a low power mode, configure the TxDAC interpolation rate, and control ADC and TxDAC power-down. The SPI provides more programmable options for both the TxDAC path (for example, coarse and fine gain control and offset control for channel matching) and the ADC path (for example, the internal duty cycle stabilizer, and twos complement data format).

The AD9861 is packaged in a 64-lead LFCSP (low profile, fine pitched, chip scale package). The 64-lead LFCSP footprint is only 9 mm * 9 mm, and is less than 0.9 mm high, fitting into tightly spaced applications such as PCMCIA cards

AD9861 Data Sheet

AD9861 Data Sheet