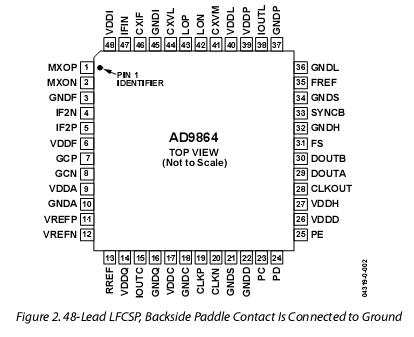

AD9864: Features: 10 MHz to 300 MHz input frequency 6.8 kHz to 270 kHz output signal bandwidth 7.5 dB SSB NF 7.0 dBm IIP3 AGC free range up to 34 dBm 12 dB continuous AGC range 16 dB front end attenuator Ba...

floor Price/Ceiling Price

- Part Number:

- AD9864

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

AD9864 Data Sheet

AD9864 Data Sheet