Features: Uses inexpensive 3.96 MHz reference crystal

FIN capability greater than 120 MHz allows direct synthesis at FM frequencies

FM resolution of either 10 kHz or 20 kHz allows usage of 10.7 MHz ceramic filter distribution

Serial data entry for simplified control

50 Hz output for time-of-day reference driven from separate low power VCCM

2 open collector buffered outputs for controlling various radio functions or loop gain

Separate AM and FM inputs; AM input has 15 mV (typical) hysteresis

Programmable charge pump current sources enable adjustment of system loop gain

Operational amplifier provides high impedance load to

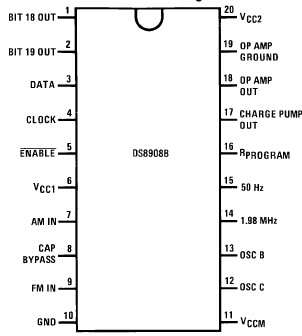

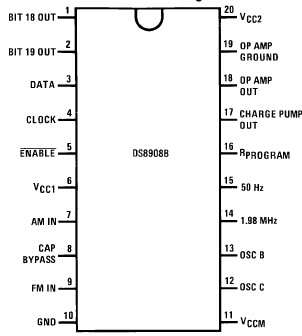

charge pump output and a wide voltage range for the VCO inputPinout SpecificationsSupply Voltage

SpecificationsSupply Voltage

(VCC1) (VCCM)............................................................... 7V

(VCC2) .........................................................................17V

Input Voltage ................................................................7V

Output Voltage .............................................................7V

Storage Temperature Range ...................-65 to +150

Lead Temperature (Soldering, 4 seconds) ..............260DescriptionThe DS8908B is a PLL synthesizer designed specifically for use in AM/FM radios. DS8908B contains the reference oscillator, a phase comparator, a charge pump, an operational amplifier, a 120 MHz ECL/I2L dual modulus programmable divider, and a 19-bit shift register/latch for serial data entry. The device DS8908B is designed to operate with a serial data controller generating the necesary division codes for each frequency, and logic state information for radio function inputs/outputs.A 3.96 MHz pierce oscillator and divider chain generate a 1.98 MHz external controller clock, a 20 kHz, 10 kHz, 9 kHz,and a 1 kHz reference signals, and a 50 Hz time-of-day signal. The DS8908B oscillator and divider chain are sourced by the VCCM pin thus providing a low power controller clock drive and time-of-day indication when the balance of the PLL is powered down.

The DS8908B 21-bit serial data steram is transferred between the frequency synthesizer and the controller via a 3-wire bus system comprised of a data line, a clock line, and an enable line.

The DS8908B first 2 bits in the serial data stream address the synthesizer thus permitting other devices such as display drivers to share the same bus. The next 14 bits are used for the PLL(Na1) divide code. The 15th bit is used internally to select the AM or FM local oscillator input. A high level on this bit enables the FM input and a low level enables the AM input. The 16th and 17th bits are used to select one of the 4 reference frequencies. The 18th and 19th bits are connected via latches to open collector outputs. These outputs can be used to drive radio functions such as gain, mute, AM, FM, or charge pump current source levels.

The PLL consists of a 14-bit programmable I2L divider, an ECL phase comparator, an ECL dual modulus (p/p a1) prescaler, a high speed charge pump, and an operational amplifier. The programmable divider divides by (Na1), N being the number loaded into the shift register. The programmable divider is clocked through a d-/8 prescaler by the AM input or through a d$*/64 prescaler by the FM input. The AM input will work at frequencies up to 15 MHz, while the FM input works up to 120 MHz. The VCO can be tuned with a frequency resolution of either 1 kHz, 9 kHz, 10 kHz, or 20 kHz.

The buffered AM and FM inputs are self-biased and can be driven directly by the VCO through a capacitor. The ECL phase comparator produces very accurate resolution of the phase difference between the input signal and the reference oscillator. The high speed charge pump consists of a switchable constant current source and sink. The charge pump can be programmed to deliver from 75 mA to 750 mA of constant current by connection of an external resistor from pin RPROGRAM to ground or the open collector bit outputs.

Connection of programming resistors to the bit outputs enables the controller to adjust the loop gain for the particular reference frequency selected. The charge pump will source current if the VCO frequency is high and sink current if the VCO frequency is low. The low noise operational amplifier provided has a high impedance JFET input and a large output voltage range. The op amp's negative input is common with the charge pump output and its positive input is internally biased.

DS8908B Data Sheet

DS8908B Data Sheet