Features: `Optimized for applications requiring large internal memory, flexible I/O, and high cycle efficiency speech coding, speech compression, and channel coding

- Large on-chip dual-port RAM (60 Kwords of DPRAM)-eliminates need for fast external SRAM

- 2-input 40-bit arithmetic logic unit (ALU) with add/compare/select (ACS) for Viterbi acceleration

- 3-input adder

- DMA-based I/O-minimizes DSP core overhead for I/O processing

- Flexible power management modes for low system power dissipation

- Provides 200 DSP MIPS

`10 ns instruction cycle time at 3 V

`Dual 16 x 16-bit multiplication and 40-bit accumulation in one instruction cycle for efficient algorithm implementations

`31-instruction by 32-bit interruptible do-loop cache for high-speed, program-efficient, zero-overhead looping

`Nested interrupts and three interrupt priority levels for efficient control and task management operations

`On-chip boot ROM with hardware development system and boot code for flexible downloading

`On-chip, programmable, PLL clock synthesizer

`Enhanced serial I/O (ESIO) port designed to multiplex/demultiplex 64 Kbits/s, 32 Kbits/s, 16 Kbits/s, and 8 Kbits/s channels

`26 Mbits/s simple serial I/O (SSIO) port coupled with DMA to support low-overhead I/O

`16-bit parallel host interface (PHIF16) coupled with DMA to support low-overhead I/O

- Supports either 8-bit or 16-bit external bus configurations (8-bit external configuration supports either 8-bit or 16-bit logical transfers)

- Supports either Motorola1 or Intel2 protocols

`8-bit control I/O interface for increased flexibility and lower system costs

`IEEE3 1149.1 test port (JTAG boundary scan)

`Full-speed in-circuit emulation hardware development system on-chip with eight address and two data watchpoint units for efficient application development

`Pin compatible with the DSP1620

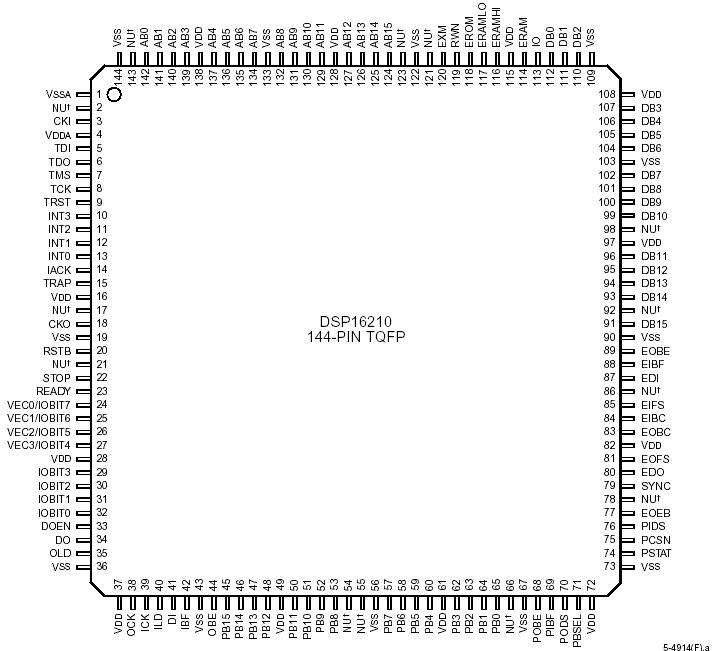

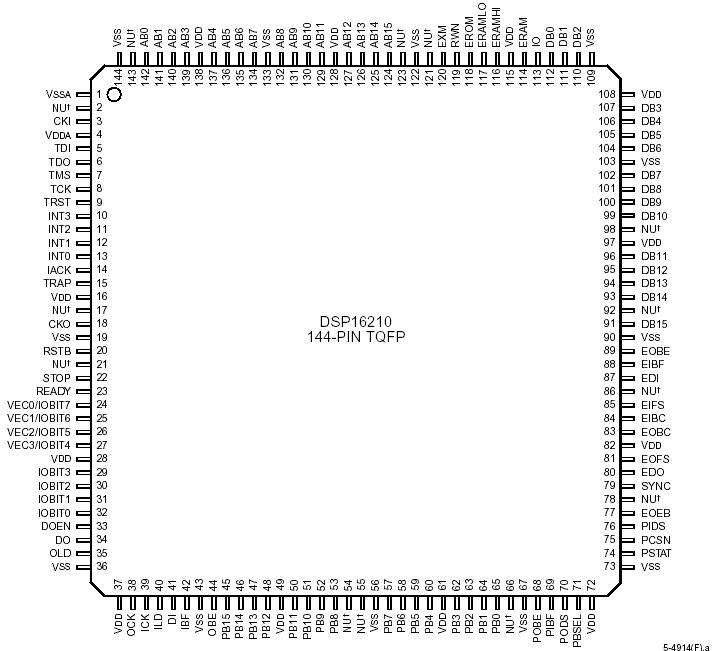

`144-pin TQFP package

Pinout Specifications

Specifications

| ParameterParameter |

Min |

Max |

Unit |

| Voltage Range on VDD or VDDA with Respect to Ground |

0.5 |

+4.6 |

V |

| Voltage Range on Any Signal Pin |

VSS 0.5 |

VDD + 0.5 |

V |

| Power Dissipation |

- |

1 |

W |

| Junction Temperature (TJ) |

40 |

+125 |

°C |

| Storage Temperature Range |

65 |

+150 |

°C |

DescriptionThe DSP16210 is the first DSP device based on the DSP16000 digital signal processing core. It is manufactured in a 0.35 mm CMOS technology and offers a 10 ns instruction cycle time at 3 V operation. Designed specifically for applications requiring a large amount of memory, a flexible DMA-based I/O structure, and high cycle efficiency, the DSP16210 is a signal coding device that can be programmed to perform a wide variety of fixed-point signal processing functions. The DSP16210 includes a mix of peripherals specifically intended to support processingintensive but cost-sensitive applications.

The large on-chip RAM (60 Kwords of dual-port RAM) supports downloadable system design-a must for infrastructure applications-to support field upgrades for evolving coding standards. The DSP16210 can address up to 192 Kwords of external storage in both its code/coefficient memory address space and data memory address space. In addition, there is an internal boot ROM (IROM) that includes system boot code and hardware development system (HDS) code.

This DSP16210 device also contains a bit manipulation unit (BMU) and a two-input, 40-bit arithmetic logic unit (ALU) with add/compare/ select (ACS) for enhanced signal coding efficiency and Viterbi acceleration.

To optimize I/O throughput and reduce the I/O service routine burden on the DSP core, the DSP16210 is equipped with two modular I/O units (MIOUs) that manage the simple serial I/O port (SSIO) and the 16-bit parallel host interface (PHIF16) peripherals. The MIOUs provide transparent DMA transfers between the peripherals and on-chip dual-port RAM.

The combination of large on-chip RAM, low power dissipation, fast instruction cycle times, and efficient I/O management makes the DSP16210 an ideal solution in a variety of emerging applications.

DSP16210 Data Sheet

DSP16210 Data Sheet