Features: • Efficient 16-bit DSP engine with dual Harvard architecture

• 120 Million Instructions Per Second (MIPS) at 120MHz core frequency

• Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

• Four (4) 36-bit accumulators including extension bits

• 16-bit bidirectional shifter

• Parallel instruction set with unique DSP addressing modes

• Hardware DO and REP loops

• Three (3) internal address buses and one (1) external address bus

• Four (4) internal data buses and one (1) external data bus

• Instruction set supports both DSP and controller functions

• Four (4) hardware interrupt levels

• Five (5) software interrupt levels

• Controller-style addressing modes and instructions for compact code

• Efficient C Compiler and local variable support

• Software subroutine and interrupt stack with depth limited only by memory

• JTAG/Enhanced OnCE debug programming interfacePinout Specifications

Specifications

| Characteristic |

Symbol |

Min |

Max |

Unit |

| Supply voltage, core |

VDD1 |

VSS 0.3 |

VSS + 2.0 |

V |

Supply voltage, IO

Supply voltage, analog |

VDDIO2

VDDIO2 |

VSSIO 0.3

VSSA 0.3 |

VSSIO + 4.0

VDDA + 4.0 |

V |

Digital input voltages

Analog input voltages (XTAL, EXTAL) |

VIN

VINA |

VSSIO 0.3

VSSA 0.3 |

VSSIO + 5.5

VDDA + 0.3 |

V |

Current drain per pin excluding VDD, VSS, VDDA,

VSSA,VDDIO, VSSIO |

I |

- |

10 |

mA |

| Junction temperature |

TJ |

-40 |

120 |

°C |

| Storage temperature range |

TSTG |

55 |

150 |

°C |

DescriptionThe DSP56852 is a member of the DSP56800E core-based family of Digital Signal Processors (DSPs). On a single chip it combines the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the DSP56852 is well-suited for many applications. The DSP56852 includes many peripherals especially useful for low-end Internet appliance applications and low-end client applications such as telephony; portable devices; Internet audio; and point-of-sale systems such as noise suppression; ID tag readers; sonic/subsonic detectors; security access devices; remote metering; and sonic alarms.

The DSP56800E core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The microprocessor-style programming model and optimized instruction set allow straightforward generation of efficient, compact code for both DSP and MCU applications. The instruction set is also highly efficient for C-Compilers, enabling rapid development of optimized control applications.

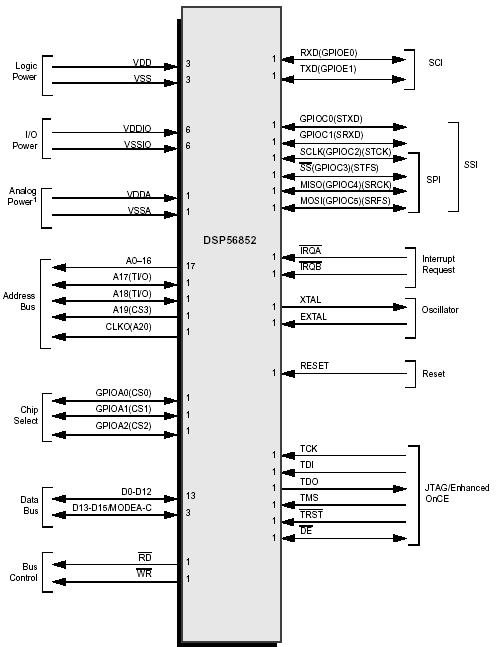

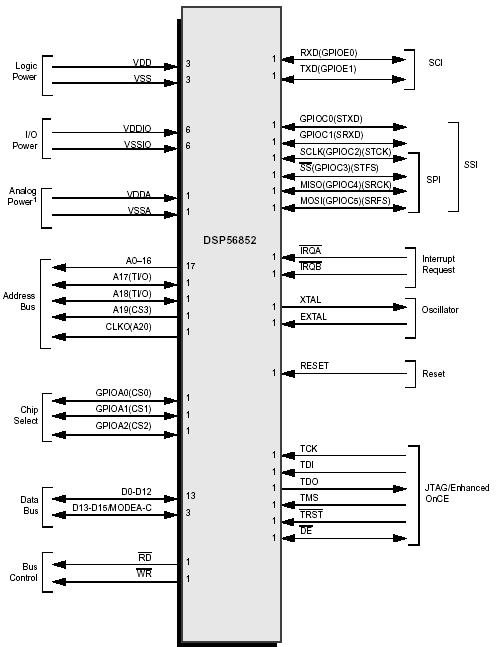

The DSP56852 supports program execution from either internal or external memories. Two data operands can be accessed from the on-chip Data RAM per instruction cycle. The DSP56852 also provides two external dedicated interrupt lines, and up to 11 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The DSP56852 DSP controller includes 6K words of Program RAM, 4K words of Data RAM and 1K of Boot RAM. It also supports program execution from external memory.

This DSP controller also provides a full set of standard programmable peripherals that include one improved Synchronous Serial Interface (SSI) or one Serial Peripheral Interface (SPI), one Serial Communications Interface (SCI), and one Quad Timer. The SSI, SPI, SCI I/O and three chip selects can be used as General Purpose Input/Outputs when its primary function is not required. The SSI and SPI share I/O, so, at most, one of these two peripherals can be in use at any time.

Digital Signal Controller

DSP56852 Data Sheet

DSP56852 Data Sheet