Programmable Type: In System Programmable

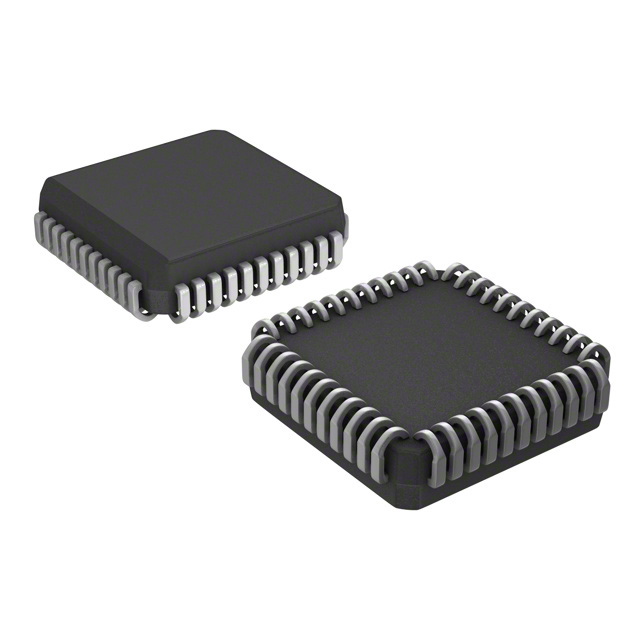

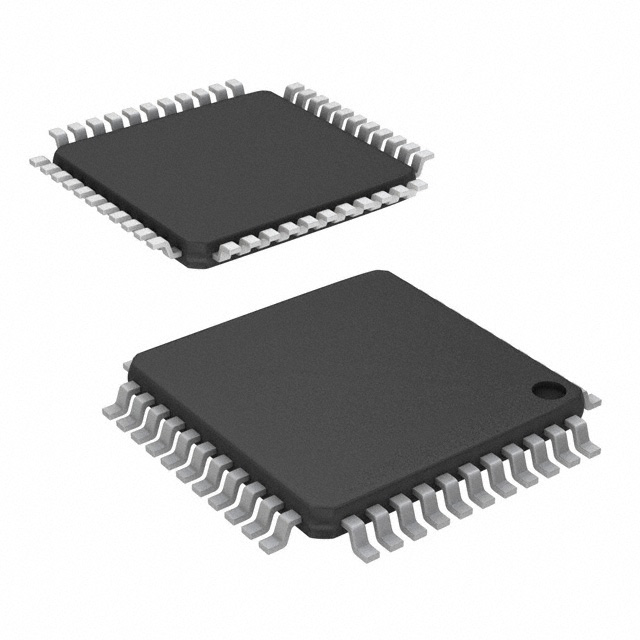

Mounting Type: Surface Mount

Package / Case: 44-TQFP

Supplier Device Package: 44-TQFP (10x10)

Packaging: Tray

Delay Time tpd(1) Max: 7.5ns

Operating Temperature: -40°C ~ 85°C

Number of Logic Elements/Blocks: 4

Number of Macrocells: 64

Voltage Supply - Internal: 4.5 V ~ 5.5 V

Manufacturer: Altera

Number of Gates: 1250

Number of I /O: 36

Series: MAX® 7000

Pinout Description

DescriptionThe EPM7064STI44-7 is designed as one member of the MAX7000S programmable logic device family which is based

on Altera's second-generation MAX architecture.

This EPM7064STI44-7 family has many features and some are lised here. (1) High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX architecture. (2) 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 joint test action group (JTAG) interface available in MAX 7000S devices ISP circuitry compatible with IEEE Std. 1532. (3) Includes 5.0-V MAX7000 devices and 5.0-V ISP-based MAX7000S devices. (4) Built-in JTAG boundary-scan test (BST) circuitry in MAX7000S devices with 128 or more macrocells. (5) Complete EPLD family with logic densities ranging from 600 to 5000 usable gates. (6) 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect). (7) PCI-compliant devices available. (8) Open-drain output option in MAX7000S devices. (9) Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls. (10) Programmable power-saving mode for a reduction of over 50% in each macrocell. (11) Configurable expander product-term distribution, allowing up to 32 product terms per macrocell. That are all the main features.

Some spedifications of EPM7064STI44-7 have been concluded into several points as follow. (1) Its usable gates would be 1250. (2) Its macrocells would be 64. (3) Its logic array blocks would be 4. (4) Its maximum user I/O pins would be 68. (5) Its tPD would be 5ns. (6) Its tSU would be 2.9ns. (7) Its tFSU would be 2.5ns. (8) Its tCO1 would be 3.2ns. (9) Its fCNT would be 175.4MHz.

Also some absolute maximum ratings about EPM7064STI44-7. (1) Its supply voltage would be min -2.0V and max 7.0V. (2) Its DC input voltage would be min -2.0V and max 7.0V. (3) Its DC output current, per pin would be min -25mA and max 25mA. (4) Its storage temperature range would be from -65°C to 135°C. (5) Its ambient temperature range would be from -65°C to 135°C. (6) Its junction temperature would be max 150°C. And so on. If you have any question or suggestion or want to know more information please contact us for details. Thank you!

Parameters: | Technical/Catalog Information | EPM7064STI44-7 |

| Vendor | Altera |

| Category | Integrated Circuits (ICs) |

| Programmable Type | In System Programmable |

| Number of Macrocells | 64 |

| Number of I /O | 36 |

| Number of Logic Blocks/Elements | 4 |

| Operating Temperature | -40°C ~ 100°C |

| Package / Case | 44-TQFP |

| Features | - |

| Voltage | 5V |

| Memory Type | EEPROM |

| Delay Time tpd(1) Max | 6.0nS |

| Packaging | Tray |

| Lead Free Status | Contains Lead |

| RoHS Status | RoHS Non-Compliant |

| Other Names | EPM7064STI44 7

EPM7064STI447

544 2023 ND

5442023ND

544-2023

|

EPM7064STI44-7 Data Sheet

EPM7064STI44-7 Data Sheet