DescriptionThe EPM7128SQC160-10N is one member of the MAX7000 series.MAX7000 devices use CMOS EEPROM cells to implement logic functions. The user-configurable MAX7000 architecture accommodates a variety of independent combinatorial and sequential logic functions. The devices can be reprogrammed for quick and efficient iterations during design development and debug cycles, and can be programmed and erased up to 100 times.

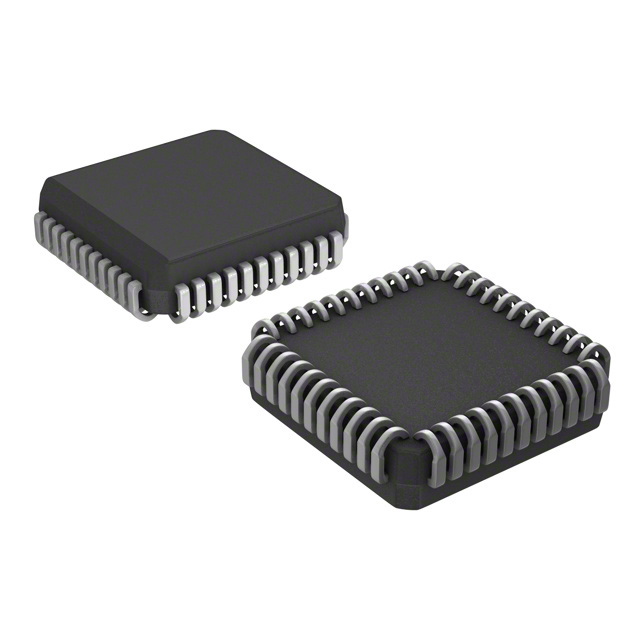

Features of the EPM7128SQC160-10N are:(1)open-drain output option in MAX7000S devices; (2)programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls; (3)programmable power-saving mode for a reduction of over 50% in each macrocell; (4)configurable expander product-term distribution, allowing up to 32 product terms per macrocell; (5)44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages; (6)programmable security bit for protection of proprietary designs.

The absolute maximum ratings of the EPM7128SQC160-10N can be summarized as:(1)supply voltage for internal logic and input buffers:4.75 to 5.25V;(2)ambient temperature:0 to +70;(3)junction temperature:0 to 90;(4)supply voltage for output drivers,5.0-V operation:4.75 to 5.25V;(5)input rise time:40ns.In-system programming can be accomplished with either an adaptive or constant algorithm. An adaptive algorithm reads information from the unit and adapts subsequent programming steps to achieve the fastest possible programming time for that unit. Because some in-circuit testers cannot support an adaptive algorithm, Altera offers devices tested with a constant algorithm. Devices tested to the constant algorithm have an "F" suffix in the ordering code.MAX7000 devices offer a power-saving mode that supports low-power operation across user-defined signal paths or the entire device. This feature allows total power dissipation to be reduced by 50% or more, because most logic applications require only a small fraction of all gates to operate at maximum frequency.

EPM7128SQC160-10N Data Sheet

EPM7128SQC160-10N Data Sheet