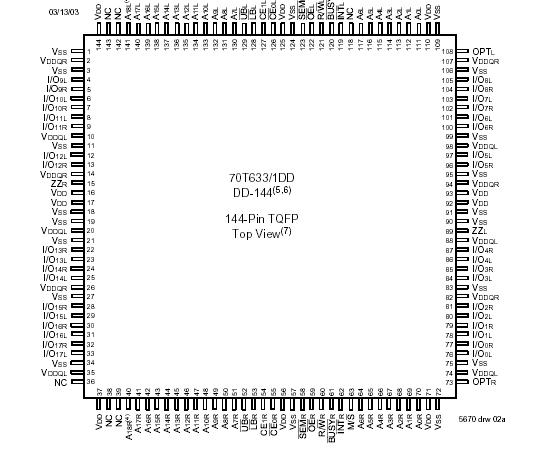

IDT70T631S: Features: On-chip port arbitration logic Fully asynchronous operation from either port Separate byte controls for multiplexed bus and bus matching compatibility Sleep Mode Inputs on both ports Supp...

floor Price/Ceiling Price

- Part Number:

- IDT70T631S

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

IDT70T631S Data Sheet

IDT70T631S Data Sheet