Features: 1.1 Video input and preprocessing

` Digital YUV input according to "ITU-R BT.656"(8 bits at 27 MHz) and "ITU-R BT.601"

` Support of enhanced "ITU-R BT.656" input format containing decoded VBI data readable via I2C-bus; Closed Caption (CC), Wide Screen Signalling (WSS) and copyright information with Copy Generation Management System (CGMS)

` Processing of non-broadcast video signals from analog VCR according to IEC 756

` Two video clock input pins for switching two digital video sources

` "ITU-R BT.601"format conversion to 1/2D1, 2/3D1 and Standard Interchange Format (SIF)

` 4 : 2 : 2 to 4 : 2 : 0 colour format conversion

` Decimation filtering for all format conversions

` Adaptive median filter and motion compensated filter for input noise reduction.

1.2 Video compression

` Real-time MPEG-2 encoding compliant to Main Profile at Main Level (MP@ML) for 625 and 525 interlaced line systems

` Supported resolutions: D1, 2/3D1, 1/2D1 and SIF

` IPB frame, IP frame and I frame only encoding supported at all modes

` Supported bit rates: up to 25 Mbit/s I-only encoding; up to 15 Mbit/s IP-only or IBP encoding.

` Variable video bit rate mode for constant picture quality and constant bit rate mode to gain optimum picture quality from a fixed channel transfer rate

` Access to bit rate control parameters whilst encoding to support external real-time control algorithms (e.g. constrained variable bit rate control)

` Programmable Group Of Pictures (GOP) structure

` Innovative motion estimation with wide search range

` Adaptive quantization

` Motion compensated noise filter.

1.3 Audio input

` Audio inputs: I2S format or EIAJ format (16, 18 or 20 bits), master or slave mode at 32, 44.1 and 48 kHz

` Two digital I2S input ports for selection between two digital audio sources

` Audio clock generation: 256fs or 384fs (where fs = 48 kHz) locked to video frame rate (if video is present and locking is enabled)

` Sample rate conversion to 48 kHz (locked to video frame rate if enabled) for slave mode operation in all modes except Digital Versatile Disc (DVD) compliant bypass.

1.4 Audio compression

` Dolbyâ(1) Digital Consumer Encoding (DDCE) also known as AC-3(2) 2 channel audio encoding at 256 kbit/s or 384 kbit/s (only for SAA6752HS/V103)

` MPEG-1 layer 2 audio encoding at 256 kbit/s or 384 kbit/s

` Input data bypass for Linear Pulse Code Modulation (LPCM) and compressed audio data [MPEG-1, MPEG-2, Dolbyâ Digital (DD) and Digital Theatre System (DTS)] according to IEC 61937

` Preamble Pc, Preamble Pd and bit stream information captured for identification of modes during bypass of compressed audio data for MPEG-1, MPEG-2, DD and DTS according to IEC 61937

` Audio mute via I2C-bus control for all modes except DVD-compliant bypass.

1.5 Stream multiplexer

` Multiplexing of video and audio streams according to MPEG-2 systems standard ( "ISO 13818-1")

` Generation and output of MPEG-2 Transport Streams (TS), MPEG-2 Program Streams (PS), Packetized Elementary Streams (PES) and Elementary Streams (ES) compliant to the DVD, D-VHS and DVB standards

` MPEG time stamp (PTS/DTS/SCR/PCR) generation and insertion (synchronization)

` Insertion of metadata

` Optional generation of empty time slots for subsequentinsertion of application specific data packets

` Optional insertion of user data in the GOP header and the picture header

` Optional automatic insertion of Closed Caption data according to DVD or ATSC standard

` Optional generation of transport streams with variable bit rate.

1.6 Output interface

` Parallel interface 8-bit master/slave output

` 3-state output port

` Glueless interfacing with IEEE 1394 chip sets (for example, PDI 1394 L11)

` Data Expansion Bus Interface (DEBI) interface.

1.7 Control domain

` All control done via I2C-bus

` I2C-bus slave transceiver up to 400 kbit/s

` I2C-bus slave address select pin

` Host interrupt flag pin.

1.8 Other features

` Single external clock or single crystal 27 MHz

` Separate 27 MHz system clock output

` Interface voltage 3.3 V

` TTL compatible digital outputs

` Power supply voltage 3.3 and 2.5 V

` Boundary Scan Test (BST) supported

` Power-down mode

` Single SDRAM system memory (16 Mbit@16 bit or 64 Mbit@16 bit).

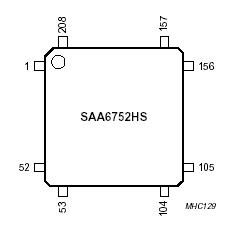

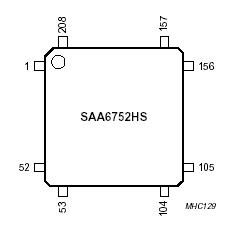

Pinout Specifications

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

MAX. |

UNIT |

VDDP

VDDCO

VDDA

VI

Vi

VO

Isc

Ilu(prot)

Ptot

Tstg

Tamb

Ves |

digital supply voltage for pads

digital supply voltage for core

analog supply voltage

digital input voltage

analog input voltage

digital output voltage

short-circuit current of output pads

latch-up protection current

total power dissipation

storage temperature

ambient temperature

electrostatic handling voltage |

note 1

note 2

note 3

note 4

note 5

note 6 |

-0.5

-0.5

-0.5

-0.5

-0.5

-0.5

-

-

-

-25

0

-2000

-150 |

+4.0

+2.8

+2.8

+4.0

+2.8

VDDP + 0.5

125

100

2

+125

70

+2000

+150 |

V

V

V

V

V

V

mA

mA

W

°C

°C

V

V |

Notes

1. All pads are not 5 V tolerant.

2. Pins XTALI and XTALO.

3. At VDDP > 3.7 V only maximum 4.2 V at digital outputs is allowed.

4. Short-circuit current is only allowed for a short time (<1 s).

5. Human body model: C = 100 pF; R = 1.5 k.

6. Machine model: C = 200 pF; L = 0.75 mH; R = 0 .DescriptionPhilips Semiconductors' second generation real time MPEG-2 encoder, the SAA6752HS, is a highly integrated single-chip audio and video encoding solution with flexible multiplexing functionality. With our expertise in two critical areas for consumer video encoding, noise filtering and motion estimation, we have pushed the boundaries for video quality even further, providing enhanced quality for low bit rates and enabling increased recording times for a given storage capacity. The SAA6752HS will also enable a key driver for new consumer digital recording applications and system cost reduction. By integrating all audio encoding and multiplexing functionality we will be moving from a three chip to a one chip system, with cost efficient design and process technology, thus providing a truly low cost, high quality encoding system.

The SAA6752HS/V104 is intended for customers whose application does not require the DDCE function. The SAA6752HS gives significant advantages to customers developing digital recording applications:

` Fast time-to-market and low development

resources. By adding a simple external video input processor IC, an audio analog-to-digital converter, and an external SDRAM, analog video and audio sources are compressed into high quality MPEG-2 video and MPEG-1 layer 2 or AC-3 audio streams, multiplexed into a single program or transport stream for simple connection to various storage media or broadcast media. Hence, making design effort for our customers a minimum, as well as removing the need for in-depth experience in MPEG encoding.

` Low system host resources. All video and audio

encoding algorithms and software are run on an internal MIPSâ(1) processor. The SAA6752HS only requires a small amount of communication from the system host processor to set up and control required encoding parameters via the I2C-bus.

SAA6752HS Data Sheet

SAA6752HS Data Sheet