Features: General Features

• Dual full-duplex synchronous/ asynchronous receiver and transmitter

• Multi-protocol operation

BOP: HDLC/ADCCP, SDLC, SDLC loop, X.25 or X.75 link level, etc.

COP: Single SYNC, dual SYNC, BiSYNC, DDCMP

ASYNC: 5-8 bits plus optional parity

• Sixteen character receive and transmit FIFOs with interrupt threshold control

• FIFO'ed status bits

• Watchdog timer

• 0 to 10 Mbit/sec data rate

• Programmable bit rate for each receiver and transmitter selectable from:

19 fixed rates: 50 to 64K baud

One user-defined rate derived from programmable counter/timer

External 1X or 16X clock

Digital phase-locked loop

• Parity and FCS (frame check sequence LRC or CRC) generation and checking

• Programmable data encoding/decoding: NRZ, NRZI, FM0, FM1, Manchester

• Programmable channel mode: full- or half-duplex, auto-echo, or local loopback

• Programmable data transfer mode: polled, interrupt, DMA, wait

• DMA interface

Compatible with Synchronous and Asynchronous bus DMA controllers

Half- or full-duplex operation

Single or dual address data transfers

Automatic frame termination on counter/ timer terminal count or DMA DONE (EOPN)

• Transmit path clear status

• High speed data bus interface: 160ns bus cycle

• DPLL operation up to 312.5kHz with internal clock

• Interrupt capabilities

Vector output (fixed or modified by status)

Individual interrupt enable bits

Programmable internal priorities

Maskable interrupt conditions

80XX/X compatible

• Multi-function programmable 16-bit counter/timer

Bit rate generator

Event counter

Count received or transmitted characters

Delay generator

Automatic bit length measurement

• Modem controls

RTS, CTS, DCD, and up to four general purpose I/O pins per channel

CTS and DCD programmable auto-enables for Tx and Rx

Programmable interrupt on change of CTS or DCD

• On-chip oscillator for crystal

• TTL compatible

• Single +5V power supply

Asynchronous Mode Features

• Character length: 5 to 8 bits

• Odd or even parity, no parity, or force parity

• Up to two stop bits programmable in 1/16-bit increments

• 1X or 16X Rx and Tx clock factors

• Parity, overrun and framing error detection

• False start bit detection

• Break generation with handshake for counting break characters

• Detection of start and end of received break

• Character compare with optional interrupt on match

• Transmit and receive up to 10Mbps at 1x or 1Mbps at 16x data rates

ApplicationApplications that are described herein for any of these products are for illustrative purposes only. Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

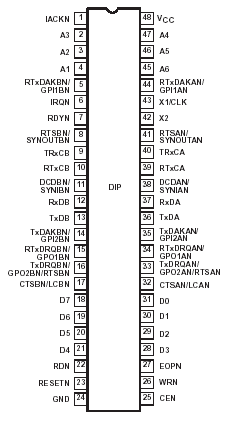

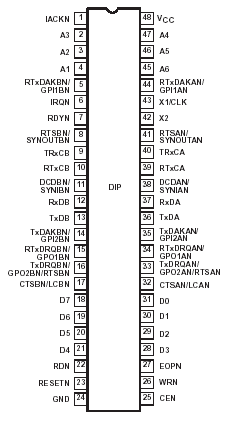

Pinout Description

DescriptionThe Philips Semiconductors SC26C562 Dual Universal Serial Communications Controller (CDUSCC) is a single-chip CMOS-LSI communications device that provides two independent, multi-protocol, full-duplex receiver/transmitter channels in a single package. It supports bit-oriented and character-oriented (byte count and byte control) synchronous data link controls as well as asynchronous protocols. The SC26C562 interfaces to synchronous bus MPUs and is capable of program-polled, interrupt driven, block-move or DMA data transfers.

The SC26C562 (CDUSCC) is (PIN) hardware and (REGISTER) software compatible with the existing SCN26562 (DUSCC). CDUSCC will automatically configure to the NMOS DUSCC register map (default mode) on power up.

The operating mode and data format of each channel can be programmed independently. Each channel consists of a receiver, a transmitter, a 16-bit multifunction counter/timer, a digital phase-locked loop (DPLL), a parity/CRC generator and checker, and associated control circuits. The two channels share a common bit rate generator (BRG), operating directly from a crystal or an external clock, which provides sixteen common bit rates simultaneously. The operating rate for the receiver and transmitter of each channel can be independently selected from the BRG, the DPLL, the counter/timer, or from an external 1X or 16X clock, making the CDUSCC well-suited for dual-speed channel applications. Data rates up to 10Mbits per second are supported.

The transmitter and receiver each contain a sixteen-deep FIFO with appended transmitter command and receiver status bits and a shift register. This permits reading and writing of up to sixteen characters at a time, minimizing the potential of receiver overrun or transmitter underrun, and reducing interrupt or DMA overhead. In addition, a flow control capability is provided to disable a remote transmitter when the FIFO of the local receiving device is full.

Two modem control inputs (DCD and CTS) and three modem control outputs (RTS and two general purpose) are provided. Because the modem control inputs and outputs are general purpose in nature, they can be optionally programmed for other functions.

The SC26C562 CDUSCC is optimized to interface with processors using a synchronous bus interface, such as the 8086, and iAPX86 family. For systems using an asynchronous bus, such as the 68000 and 68010, refer to the SC68C562 documentation.

Refer to the CMOS Dual Universal Serial Communication Controller (CDUSCC) User's Manual for a complete operational description.

SC26C562 Data Sheet

SC26C562 Data Sheet