Features: ` Members of Texas Instruments Broad Family of Testability Products Supporting IEEE Std 1149.1-1990 (JTAG) Test Access Port (TAP) and Boundary-Scan Architecture

` Extend Scan Access From Board Level to Higher Levels of System Integration

` Promote Reuse of Lower-Level (Chip/Board) Tests in System Environment

` Switch-Based Architecture Allows Direct Connect of Primary TAP to Secondary TAP

` Primary TAP Is Multidrop for Minimal Use of Backplane Wiring Channels

` Simple Addressing (Shadow) Protocol Is Received/Acknowledged on Primary TAP

` Shadow Protocols Can Occur in Any of Test-Logic-Reset, Run-Test/Idle, Pause-DR, and Pause-IR TAP States to Provide for Board-to-Board Test and Built-In Self-Test

` 10-Bit Address Space Provides for Up to 1021 User-Specified Board Addresses

` Bypass (BYP) Pin Forces Primary-to-Secondary Connection Without Use of Shadow Protocols

` Connect (CON) Pin Provides Indication of Primary-to-Secondary Connection

` High-Drive Outputs (32-mA IOH, 64-mA IOL) Support Backplane Interface at Primary and High Fanout at Secondary

` Package Options Include Plastic Small- Outline (DW) and Thin Shrink Small- Outline (PW) Packages, Ceramic Chip Carriers (FK), and Ceramic DIPs (JT)

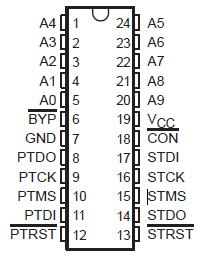

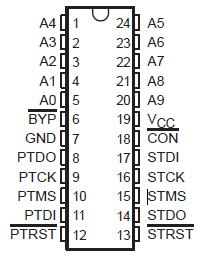

Pinout

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 7 V

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 7 V

Voltage range applied to any output in the high state or power-off state, VO . . . . . . . . ..0.5 V to 5.5 V

Current into any output in the low state, IO: SN54ABT8996 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96 mA

SN74ABT8996 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128 mA

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 mA

Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Package thermal impedance, JA (see Note 2): DW package . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81°C/W

PW package . . . . . . . . . . . . . . . . . . . . . . . . . . . 120°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65°C to 150°C

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings can be exceeded if the input and output clamp-current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51.

DescriptionThe 'ABT8996 10-bit addressable scan ports (ASP) are members of the Texas Instruments (TITM) SCOPETM testability integrated-circuit family. This 'ABT8996 family of devices supports IEEE Standard 1149.1-1990 boundary scan to facilitate testing of complex circuit assemblies. Unlike most SCOPETM devices, the ASP is not a boundary-scannable device, rather, it applies TI's addressable-shadow-port technology to the IEEE Standard 1149.1-1990 (JTAG) test access port (TAP) to extend scan access beyond the board level.

Conceptually, the 'ABT8996 ASP is a simple switch that can be used to directly connect a set of multidrop primary TAP signals to a set of secondary TAP signals for example, to interface backplane TAP signals to a board-level TAP. The ASP provides all signal buffering that might be required at these two interfaces. When primary and secondary TAPs are connected, only a moderate propagation delay is introduced no storage/retiming elements are inserted. This minimizes the need for reformatting board-level test vectors for in-system use.

SN74ABT8996 Data Sheet

SN74ABT8996 Data Sheet