Features: ` EPICE (Enhanced-Performance Implanted CMOS) Process

` Inputs Are TTL-Voltage Compatible

` 8-Bit Serial-In, Parallel-Out Shift Registers With Storage

` Independent Direct Overriding Clears on Shift and Storage Registers

` Independent Clocks for Both Shift and Storage Registers

` Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

` ESD Protection Exceeds JESD 22

2000-V Human-Body Model (A114-A)

200-V Machine Model (A115-A)

1000-V Charged-Device Model (C101)

` Package Options Include Plastic Small-Outline (D), Shrink Small-Outline (DB), Thin Shrink Small-Outline (PW), and Ceramic Flat (W) Packages, Ceramic Chip Carriers (FK), and Standard Plastic (N) and Ceramic (J) DIPs

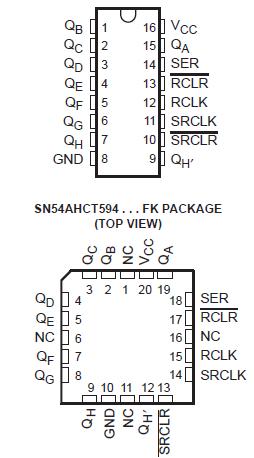

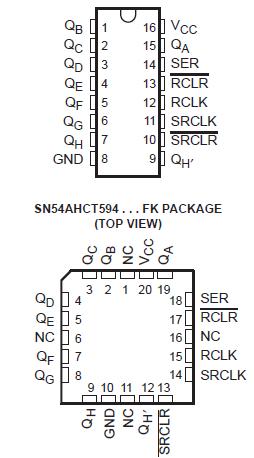

Pinout Specifications

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 7 V

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . 0.5 V to 7 V

Output voltage range, VO (see Note 1) . . . . . . 0.5 V to VCC + 0.5 V

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . 20 mA

Output clamp current, IOK (VO < 0 or VO > VCC) . . . . . . . . . . ±20 mA

Continuous output current, IO (VO = 0 to VCC) . . . . . . . . . . . ±25 mA

Continuous current through VCC or GND . . . . . . . . . . . . . .. . . ±50 mA

Package thermal impedance, JA (see Note 2): D package . . 73°C/W

DB package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82°C/W

N package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67°C/W

PW package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . .. 65°C to 150°C

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51.

DescriptionThe 'AHCT594 devices contain an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. Separate clocks and direct overriding clear (SRCLR, RCLR) inputs are provided on both the shift and storage registers. A serial (QH') output is provided for cascading purposes.

Both the 'AHCT594 shift register (SRCLK) and storage register (RCLK) clocks are positive edge triggered. If both clocks are connected together, the shift register always is one count pulse ahead of the storage register.The SN54AHCT594 is characterized for operation over the full military temperature range of 55°C to 125°C.

The SN74AHCT594 is characterized for operation from 40°C to 85°C.

SN74AHCT594 Data Sheet

SN74AHCT594 Data Sheet