Features: · Independent Asychronous Inputs and Outputs

· 16 Words by 5 Bits

· Data Rates From up to 40 MHz

· Fall-Through Time 14 ns Typ

· 3-State Outputs

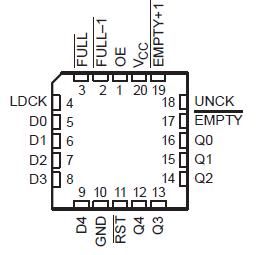

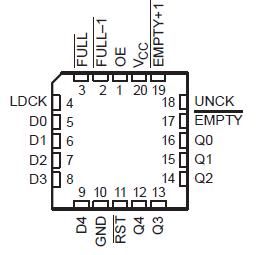

· Package Options Include Plastic Small-Outline Package (DW), Plastic Chip Carriers (FN), and Standard Plastic 300-mil DIPs (N)Pinout Specifications

SpecificationsSupply voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . 7 V

Input voltage, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Voltage applied to a disabled 3-state output . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . 5.5 V

Package thermal impedance, JA (see Note 1): DW package . . . . . . . . . . . . . . . . . . 97°C/W

FN package . . . . . . . . . . . . . . . . . . . 83°C/W

N package . . . . . . . . . . . . . . . . . . . . 67°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65°C to 150°C

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The package thermal impedance is calculated in accordance with JESD 51, except for through-hole packages, which use a trace length of zero.

DescriptionThis SN74ALS233B 80-bit memory uses advanced low-power Schottky technology and features high speed and a fast fall-through time. It is organized as 16 words by 5 bits.

A SN74ALS233B FIFO memory is a storage device that allows data to be written into and read from its array at independent data rates. This FIFO is designed to process data at rates up to 40 MHz in a bit-parallel format, word by word.

Data of SN74ALS233B is written into memory on a low-to-high transition at the load clock (LDCK) input and is read out on a low-to-high transition at the unload clock (UNCK) input. The memory is full when the number of words clocked in exceeds by 16 the number of words clocked out. When the memory is full, LDCK signals have no effect. When the memory is empty, UNCK signals have no effect.

Status of the SN74ALS233B FIFO memory is monitored by the FULL, EMPTY, FULL1, and EMPTY+1 output flags. The FULL output is low when the memory is full and high when it is not full. The FULL1 output is low when the memory contains 15 data words. The EMPTY output is low when the memory is empty and high when it is not empty. The EMPTY+1 output is low when one word remains in memory.

A low level on the reset (RST) input resets the internal stack control pointers and also sets EMPTY low and sets FULL, FULL1, and EMPTY+1 high. The Q outputs are not reset to any specific logic level. The first low-to-high transition on LDCK, after either a RST pulse or from an empty condition, causes EMPTY to go high and the data to appear on the Q outputs. It is important to note that the first word does not have to be unloaded. Data outputs are noninverting with respect to the data inputs and are at high impedance when the output-enable (OE) input is low. OE does not affect the output flags. Cascading is easily accomplished in the word-width direction but is not possible in the word-depth direction.The SN74ALS233B is characterized for operation from 0°C to 70°C.

SN74ALS233B Data Sheet

SN74ALS233B Data Sheet