Features: ` Member of the Texas Instruments WidebusTM Family

` EPICTM (Enhanced-Performance Implanted CMOS) Submicron Process

` Output Ports Have Equivalent 26- Series Resistors, So No External Resistors Are Required

` ESD Protection Exceeds 2000 V Per MIL-STD-833, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

` Latch-Up Performance Exceeds 250 mA Per JESD 17

` Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

` Package Options Include Plastic 300-mil Shrink Small-Outline (DL) and Thin Shrink Small-Outline (DGG) Packages

NOTE: For tape and reel order entry:

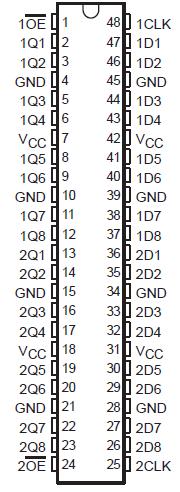

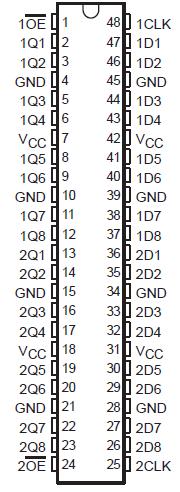

The DGGR package is abbreviated to GR.Pinout Specifications

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 0.5 V to 4.6 V

Output voltage range, VO (see Notes 1 and 2) . . . . . . . . . . . . . .. . 0.5 V to VCC + 0.5 V

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Continuous output current, IO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . ±50 mA

Continuous current through each VCC or GND . . . . . . . . . . . . . . . . . . . . . . . . . . . ±100 mA

Package thermal impedance, JA (see Note 3): DGG package . . . . . . . . . .. . . . . . 89°C/W

DL package . . . . . . . . . . .. . . . . . 94°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65°C to 150°C

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. This value is limited to 4.6 V maximum.

3. The package thermal impedance is calculated in accordance with JESD 51.

DescriptionThis SN74ALVCH162374 16-bit edge-triggered D-type flip-flop is designed for 1.65-V to 3.6-V VCC operation.

The SN74ALVCH162374 is particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers. It can be used as two 8-bit flip-flops or one 16-bit flip-flop. On the positive transition of the clock (CLK) input, the Q outputs of the flip-flop take on the logic levels set up at the data (D) inputs.

The output-enable (OE) input of SN74ALVCH162374 can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and the increased drive provide the capability to drive bus lines without need for interface or pullup components. OE does not affect internal operations of the flip-flop. Old data can be retained or new data can be entered while the outputs are in the high-impedance state. The outputs, which are designed to sink up to 12 mA, include equivalent 26-W resistors to reduce overshoot and undershoot.

To ensure the high-impedance state of SN74ALVCH162374 during power up or power down, OE should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver. Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The SN74ALVCH162374 is characterized for operation from 40°C to 85°C.

SN74ALVCH162374 Data Sheet

SN74ALVCH162374 Data Sheet