Features: 5- Switch Connection Between Two Ports

Isolation Under Power-Off Conditions

B-Port Outputs Are Precharged by Bias Voltage to Minimize Signal Distortion During Live Insertion

ESD Protection Exceeds 2000 V Per MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

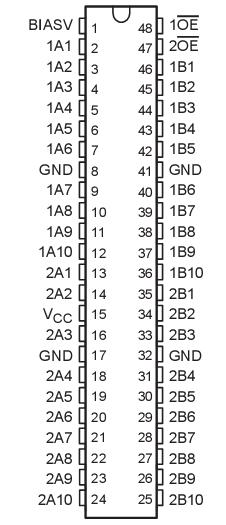

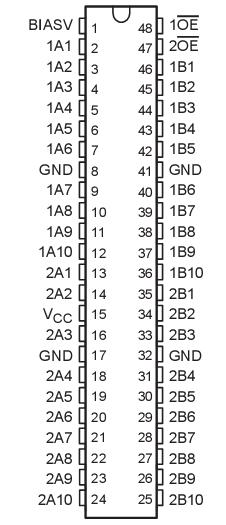

Package Options Include Plastic Thin Shrink Small-Outline (DGG), Thin Very Small-Outline (DGV), and 300-mil Shrink Small-Outline (DL) Packages

NOTE: For tape and reel order entry:

The DGGR package is abbreviated to GR, and the DGVR package is abbreviated to VR.Pinout SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

Bias voltage range, BIASV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

Continuous channel current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128 mA

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Package thermal impedance, JA (see Note 2): DGG package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89°C/W

DGV package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93°C/W

DL package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . 65 to 150

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51.DescriptionThe SN74CBTLV16800 provides 20 bits of high-speed bus switching. The low on-state resistance of the switch allows connections to be made with minimal propagation delay. The device also precharges the B port to a user-selectable bias voltage (BIASV) to minimize live-insertion noise.

The SN74CBTLV16800 is organized as dual 10-bit bus switches with separate output-enable (OE ) inputs. It can be used as two 10-bit bus switches or one 20-bit bus switch. When OE is low, the associated 10-bit bus switch is on, and port A is connected to port B. When OE is high, the switch is open, the high-impedance state exists between the two ports, and port B is precharged to BIASV through the equivalent of a 10-k resistor.

To ensure the high-impedance state during power up or power down, OE should be tied to V

CC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN74CBTLV16800 is characterized for operation from 40 to 85.

SN74CBTLV16800 Data Sheet

SN74CBTLV16800 Data Sheet