Features: Members of the Texas Instruments (TIE) WidebusTM Family

UBT TM (Universal Bus Transceiver) Combines D-Type Latches and D-Type Flip-Flops for Operation in Transparent, Latched, Clocked, or Clock-Enabled Mode

Translate Between GTLP Signal Levels and LVTTL Logic Levels

Support Mixed-Mode (3.3 V and 5 V) Signal Operation on A-Port and Control Inputs

B-Port Transition Time Optimized for Distributed Backplane Loads

Ioff Supports Partial-Power-Down Mode Operation

Bus Hold on A-Port Inputs Eliminates the Need for External Pullup/Pulldown Resistors

Distributed VCC and GND Pins Minimize High-Speed Switching Noise

ESD Protection Exceeds JESD 22

2000-V Human-Body Model (A114-A)

200-V Machine Model (A115-A)

1000-V Charged-Device Model (C101)

Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

Package Options Include Plastic Shrink Small-Outline (DL), and Thin Shrink Small-Outline (DGG) Packages

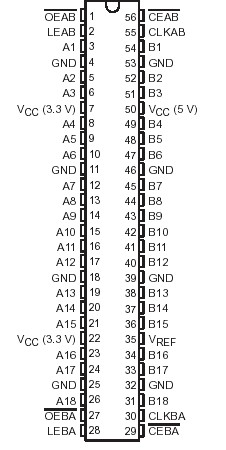

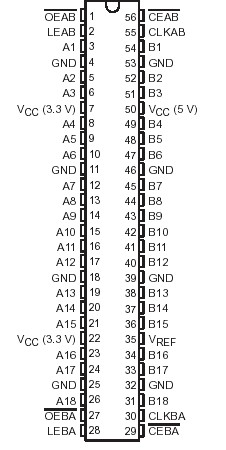

Pinout SpecificationsSupply voltage range, VCC: 3.3 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

SpecificationsSupply voltage range, VCC: 3.3 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

5 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 7 V

Input voltage range, VI (see Note 1): A-port and control inputs . . . . . . . . . . . .. . . . . . . . .0.5 V to 7 V

B port and VREF. . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4.6 V

Voltage range applied to any output in the high or power-off state, VO

(see Note 1): A port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to 7 V

B port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . 0.5 V to 4.6 V

Current into any output in the low state, IO: A port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128 mA

B port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80 mA

Current into any A-port output in the high state, IO (see Note 2) . . . . . . . . . . . . . . . . . . . . .. . . . .64 mA

Continuous current through each VCC or GND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . ±100 mA

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . .50 mA

Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 mA

Package thermal impedance, JA (see Note 3): DGG package . . . . . . . . . . . . . . . . . . . . . . . . . . . .64°C/W

DL package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . 65°C to 150°CDescriptionThe SN74GTLPH16612 is a medium-drive, 18-bit UBT (universal bus transceiver) that provides LVTTL-to-GTLP and GTLP-to-LVTTL signal-level translation. It allows for transparent, latched, clocked, or clock-enabled modes of data transfer. This device provides a high-speed interface between cards operating at LVTTL logic levels and backplanes operating at GTLP signal levels. High-speed (about two times faster than standard LVTTL or TTL) backplane operation is a direct result of the reduced output swing (<1 V), reduced input threshold levels, and OECTM (output edge control). These improvements minimize bus settling time and have been designed and tested using several backplane models.

Figure 1 of the SN74GTLPH16612 shows actual device output waveforms using a synchronous clock at 75 MHz. The test backplane is a 16-slot, 14-inch board with loaded impedance of 33 . VTT is 1.5 V, VREF is 1 V, and RTT pullup resistor is 50 W. The driver is in slot 8, with receivers in alternate slots 1, 3, 5, 7, 10, 12, 14, and 16. Receiver slot 1 signals are shown. The signal becomes progressively worse as the receiver moves closer to the driver or the spacing between receiver cards is reduced. The clock is independent of the data and the system clock frequency is limited by the backplane flight time to about 80 MHz to 90 MHz. This frequency can be increased even more (30% to 40%) if the clock is generated and transmitted together with the data from the driver card (source synchronous).

The SN74GTLPH16612 is a medium-drive (34 mA), 18-bit universal bus transceiver, containing D-type latches and D-type flip-flops to allow data flow in transparent, latched, clocked, and clock-enabled modes. This UBT can replace any of the functions shown in Table 1.

SN74GTLPH16612 Data Sheet

SN74GTLPH16612 Data Sheet