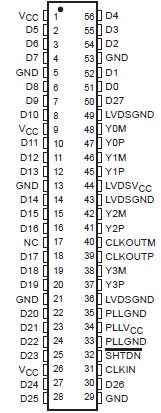

SN75LVDS81: Features: · 28:4 Data Channel Compression at up to 227.5 Million Bytes per Second Throughput· Suited for SVGA, XGA, or SXGA Display Data Transmission From Controller to Display With Very Low EMI· 28...

floor Price/Ceiling Price

- Part Number:

- SN75LVDS81

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

SN75LVDS81 Data Sheet

SN75LVDS81 Data Sheet