Features: • Organized as 64K x16 Flash + 16K x16 SRAM

• Single 3.0-3.6V Read and Write Operations(2.7-3.6V without concurrent operation)

• Concurrent Operation

Read from or write to SRAM while erase/program Flash

• Superior Reliability

Endurance: 100,000 Cycles (typical)

Greater than 100 years Data Retention

• Low Power Consumption:

Active Current: 10 mA (typical) for Flash or SRAM Read

Standby Current: 5 A (typical)

• Sector Erase Capability

Uniform 2 KWord sectors

• Fast Read Access Times:

Flash: 35 ns

SRAM: 15 and 25 ns

• Latched Address and Data for Flash

• Flash Fast Sector Erase and Word Program:

Sector Erase Time: 18 ms typical

Bank Erase Time: 70 ms typical

Word Program Time: 14 s typical

Bank Rewrite Time: 2 seconds typical

• Flash Automatic Erase and Program Timing

Internal VPP Generation

• Flash End of Write Detection

Toggle Bit

Data# Polling

• CMOS I/O Compatibility

• JEDEC Standard Command Set

• Packages Available

40-Pin TSOP (10mm x 14mm)Pinout SpecificationsTemperature Under Bias .................................................................................................. -55 to +125

SpecificationsTemperature Under Bias .................................................................................................. -55 to +125

Storage Temperature ........................................................................................................... -65 to +150

D. C. Voltage on Any Pin to Ground Potential .................................................................. -0.5V to VDD+ 0.5V

Transient Voltage (<20 ns) on Any Pin to Ground Potential ......................................... .. -1.0V to VDD+ 1.0V

Voltage on A9 Pin to Ground Potential ................................................................................ -0.5V to 13.2V

Package Power Dissipation Capability (Ta = 25) ............................................................................... 1.0W

Surface Mount Lead Soldering Temperature (3 Seconds) ............................................................... .... 240

Output Short Circuit Current(1) .................................................................................................... ..... 50 mADescriptionThe SST31LH103 ComboMemory device integrates a 64K x16 CMOS flash memory bank with a 16K x16 CMOS SRAM memory bank in a monolithic silicon,manufactured with SST's proprietary, high performance SuperFlash technology. The SST31LH103 device writes(SRAM or programs or erases flash) with a 3.0-3.6V power supply. The monolithic SST31LH103 device conforms to JEDEC standard Software Data Protect (SDP) commands.

Featuring high performance word program, the flash memory bank provides a maximum word program time of 20 sec. The entire flash memory bank can be erased and programmed word-by-word in typically 2 seconds, when using interface features such as Toggle Bit or Data# Polling to indicate the completion of Program operation. To protect against inadvertent flash write, the SST31LH103 device has on-chip hardware and softwaredata protection schemes. Designed, manufactured,and tested for a wide spectrum of applications, the SST31LH103 device is offered with a guaranteed endurance of 10,000 cycles. Data retention is rated at greater than 100 years.

The SST31LH103 operates as two independent memory banks with respective bank enable signals. The SRAM and Flash memory banks are superimposed in the same memory address space. Both memory banks share common address lines, data lines, WE# and OE#. The memory bank selection is done by memory bank enable signals. The SRAM bank enable signal, BES# selects the SRAM bank and the flash memory bank enable signal, BEF# selects the flash memory bank. The WE# signal has to be used with Software Data Protection (SDP) command sequence when controlling the Erase and Program operations in the flash memory bank. The SDP command sequence protects the data stored in the flash memory bank from accidental alteration.

The SST31LH103 provides the added functionality of being able to simultaneously read from or write to the SRAM bank while erasing or programming in the flash memory bank. The SRAM memory bank can be read or written while the flash memory bank performs Sector Erase, Bank Erase, or Word Program concurrently. All flash memory Erase and Program operations will automatically latch the input address and data signals and complete the operation in background without further input stimulus requirement. Once the internally controlled erase or program cycle in the flash bank has commenced, the SRAM bank can be accessed for read or write.

The SST31LH103 device is suited for applications that use both nonvolatile flash memory and volatile SRAM memory to store code or data. For all system applications,the SST31LH103 device significantly improves performance and reliability, while lowering power consumption,when compared with multiple chip solutions.The SST31LH103 inherently uses less energy during erase and program than alternative flash technologies.The total energy consumed is a function of the applied voltage, current, and time of application. Since for any given voltage range, the SuperFlash technology uses less current to program and has a shorter erase time, the total energy consumed during any Erase or Program operation is less than alternative flash technologies. The monolithic ComboMemory eliminates redundant functions when using two separate memories of similar architecture; therefore, reducing the total power consumption.

The SuperFlash technology provides fixed Erase and\Program times, independent of the number of Erase/Program cycles that have occurred. Therefore the system software or hardware does not have to be modified or de-rated as is necessary with alternative flash technologies,whose Erase and Program times increase with accumulated Erase/Program cycles.

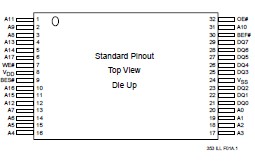

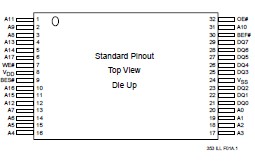

The SST31LH103 device also improves flexibility by using a single package and a common set of signals to perform functions previously requiring two separate devices. To meet high density, surface mount requirements, the SST31LH103 device is offered in a 40-pin TSOP package. See Figure 1 for pinout.

SST31LH103 Data Sheet

SST31LH103 Data Sheet