Features: RECEIVER AND DRIVERS MEET OR EXCEED THE REQUIREMENTS OF ANSI EIA/TIA-644 STANDARD: RECEIVERS LOW-VOLTAGE TTL (LVTTL) LEVELS DESIGNED FOR SIGNALING RATES UP TO 630Mbps

OPERATES FROM A SINGLE 3.3V SUPPLY

LOW VOLTAGE DIFFERENTIAL SIGNALING WITH TYPICAL OUTPUT VOLTAGE OF 350mV AND A 100W LOAD

PROPAGATION DELAY TIME: 2.2ns (TYP)

ELECTRICALLY COMPATIBLE WITH LVDS,PECL, LVPECL, LVTTL, LVCOMOS, GTL,BTL, CTT, SSTL, OR HSTL OUTPUTS WITH EXTERNAL NETWORK

BUS TERMINAL ESD (HBM) EXCEEDS 7KV

SO AND TSSOP PACKAGING

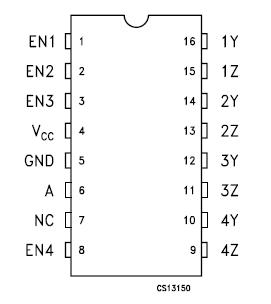

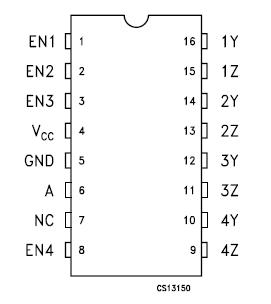

Pinout Specifications

Specifications

| Symbol |

Parameter |

Value |

Unit |

| VCC |

Supply Voltage(Note 1) |

-0.5 to 4 |

V |

| VR |

Voltage Range |

Enable Inputs |

-0.5 to 6 |

V |

| A, Y or Z |

-0.5 to 4 |

V |

| ESD |

ESD Protection Voltage (HBM) |

Y, Z, to GND |

± 7 |

KV |

| All Pins |

± 2 |

| Tstg |

Storage Temperature Range |

-65 to +150 |

|

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

Note 1: All voltages except differential I/O bus voltage, are with respect to the network ground terminal.

DescriptionThe STLVDS105 is a differential line receiver and a LVTTL input connected to four differential line drivers that implement the electrical characteristics of low voltage differential signaling,for point to point baseband data transmission over controlled impedance media of approximately 100W. The transmission media can be printed-circuit board traces, backplanes, or cable.LVDS, as specified in EIA/TIA-644 is a data signaling technique that offers low-power, low noise coupling, and switching speed to transmit data at a speed up to 630Mbps at relatively long distances.

The drivers STLVDS105 integrated into the same substrate,along with the low pulse skew of balanced signaling, allow extremely precise timing alignment of the signals repeated from the input.The device allows extremely precise timing alignment of the signal repeated from the input.This is particularly advantageous in distribution or expansion of signals such as clock or serial data stream.

STLVDS105 Data Sheet

STLVDS105 Data Sheet