Features: ` Selectable output frequencies ranging from 8 kHz to 1050 MHz

` Ultra-low jitter clock outputs w/jitter generation as low as 0.3 ps rms (50 kHz80 MHz)

` Integrated loop filter with selectable loop bandwidth (60 Hz to 8.4 kHz)

` Meets OC-192 GR-253-CORE jitter specifications

` Four clock inputs w/manual or automatically controlled hitless switching

` Five clock outputs with selectable signal format (LVPECL, LVDS, CML, CMOS)

` SONET frame sync switching and regeneration

` Support for ITU G.709 FEC ratios (255/238, 255/237, 255/236)

` LOL, LOS, FOS alarm outputs

` Pin-controlled output phase adjust

` Pin-programmable settings

` On-chip voltage regulator for 1.8 or 2.5 V ±10% operation

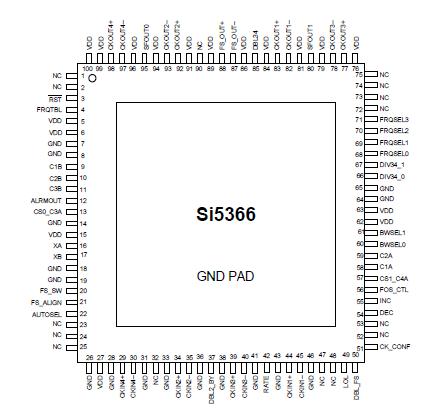

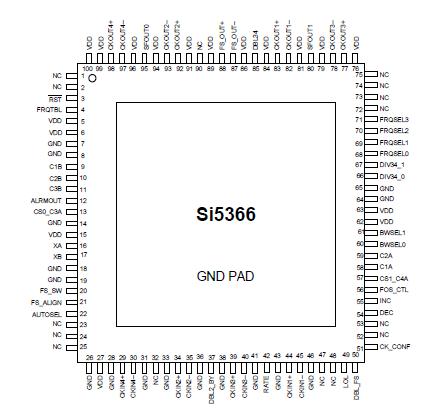

` Small size: 14 x 14 mm 100-pin TQFP

` Pb-free, RoHS compliant

Application· SONET/SDH OC-48/OC-192 line cards

· GbE/10GbE, 1/2/4/8/10GFC line cards

· ITU G.709 line cards

· Optical modules

· Test and measurementPinout Specifications

Specifications

|

Parameter |

Symbol |

Value |

Unit |

| DC Supply Voltage |

VDD |

0.5 to 2.75 |

V |

| LVCMOS Input Voltage |

VDIG |

0.3 to (VDD + 0.3) |

V |

| Operating Junction Temperature |

TJCT |

55 to 150 |

ºC |

| Storage Temperature Range |

TSTG |

55 to 150 |

ºC |

| ESD HBM Tolerance (100 pF, 1.5 k) |

|

2 |

kV |

| ESD MM Tolerance |

|

200 |

V |

| Latch-Up Tolerance |

|

JESD78 Compliant |

| Note: Permanent device damage may occur if the Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability. |

DescriptionThe Si5366 is a jitter-attenuating precision clock multiplier for high-speed communication systems, including SONET OC-48/OC-192, Ethernet, and Fibre Channel. The Si5366 accepts four clock inputs ranging from 8 kHz to 707 MHz and generates five frequencymultiplied clock outputs ranging from 8 kHz to 1050 MHz. The input clock frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, and Fibre Channel rates. The Si5366 is based on Silicon Laboratories' 3rdgeneration DSPLL® technology, which provides anyrate frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The DSPLL loop bandwidth is digitally programmable, providing jitter performance optimization at the application level. Operating from a single 1.8 or 2.5 V supply, the Si5366 is ideal for providing clock multiplication and jitter attenuation in high performance timing applications.

Si5366 Data Sheet

Si5366 Data Sheet