Features: Complete 10-Bit, 40 MSPS Dual Transmit DAC

Excellent Gain and Offset Matching

Differential Nonlinearity Error: 0.5 LSB

Effective Number of Bits: 9.5

Signal-to-Noise and Distortion Ratio: 59 dB

Spurious-Free Dynamic Range: 71 dB

23 Interpolation Filters

20 MSPS/Channel Data Rate

Single Supply: +2.7 V to +5.5 V

Low Power Dissipation: 200 mW (+3 V Supply @40 MSPS)

On-Chip Reference

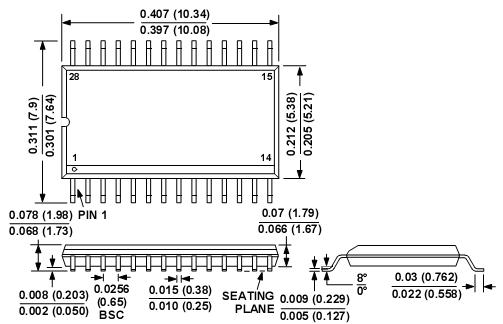

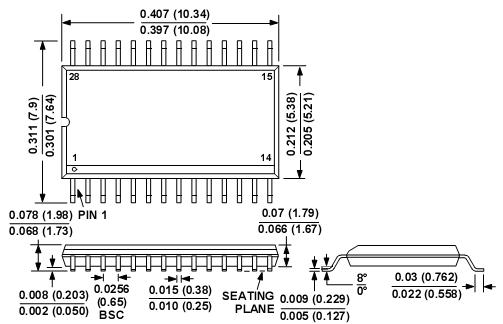

28-Lead SSOPPinout

Specifications

Specifications

| Resolution (Bits) |

10bit |

| DAC Update Rate |

40MSPS |

| DAC Settling Time |

35ns |

| # DAC Outputs |

2 |

| DAC Type |

Current Out |

| DAC Input Format |

Par |

| Output FSR |

(Iout x Rload),Adj(Uni 2mA to Uni 20mA),User Def. Range/Offset |

| Ref Int/Ext |

Int/Ext |

| Supply Vnom |

Single(+5) |

| Pwr Diss |

250mW |

| Package |

SOP |

| Parameter |

With Respectto |

Min |

Max |

Units |

AVDD

DVDD

ACOM

AVDD

CLOCK, WRITE

SELECT, SLEEP

Digital Inputs

IOUTA, IOUTB

QOUTA, QOUTB

COMP1, COMP2

COMP3

REFIO, FSADJ

REFLO

Junction Temperature

Storage Temperature

Lead Temperature (10 sec) |

ACOM

DCOM

DCOM

DVDD

DCOM

DCOM

DCOM

ACOM

ACOM

ACOM

ACOM

ACOM

ACOM |

0.3

0.3

0.3

6.5

0.3

0.3

0.3

1.0

1.0

0.3

0.3

0.3

0.3

65 |

+6.5

+6.5

+0.3

+6.5

DVDD+0.3

DVDD+0.3

DVDD+0.3

AVDD+0.3

AVDD+0.3

AVDD+0.3

AVDD+0.3

AVDD+0.3

+0.3

+150

+150

+300 |

V

V

V

V

V

V

V

V

V

V

V

V

V

|

DescriptionThe AD9761 is a complete dual channel, high speed, 10-bit CMOS DAC. The AD9761 has been developed specifically for use in wide bandwidth communication applications (e.g., sprea

spectrum) where digital I and Q information is being processed during transmit operations. It integrates two 10-bit, 40 MSPS DACs, dual 2· interpolation filters, a voltage reference, and

digital input interface circuitry. The AD9761 supports a 20MSPS per channel input data rate that is then interpolated by 2· up to 40 MSPS before simultaneously updating each DAC.

The interleaved I and Q input data stream is presented to the digital interface circuitry, which consists of I and Q latches as well as some additional control logic. The data is de-interleaved back into its original I and Q data. An on-chip state machine ensures thproper pairing of I and Q data. The data output from each latch is then processed by a 2· digital interpolation filter that eases the reconstruction filter requirements. The interpolated output of each filter serves as the input of their respective 10-bit DAC.

The DACs utilize a segmented current source architecture com bined with a proprietary switching technique to reduce glitch energy and to maximize dynamic accuracy. Each DAC provides

differential current output thus supporting single-ended or differential applications. Both DACs are simultaneously up-dated and provide a nominal full-scale current of 10 mA. Also, the full-scale currents between each DAC are matched to within 0.07 dB (i.e., 0.75%), thus eliminating the need for additional gain calibration circuitry.

The AD9761 is manufactured on an advanced low cost CMOS process. It operates from a single supply of 2.7 V to 5.5 V and consumes 200 mW of power. To make the AD9761 complete it

also offers an internal 1.20 V temperature-compensated bandgap reference.

AD9761 Data Sheet

AD9761 Data Sheet