Features: `300 MHz, 3.3 ns instruction cycle rate

`6M bits of internal-on-chip-SRAM memory

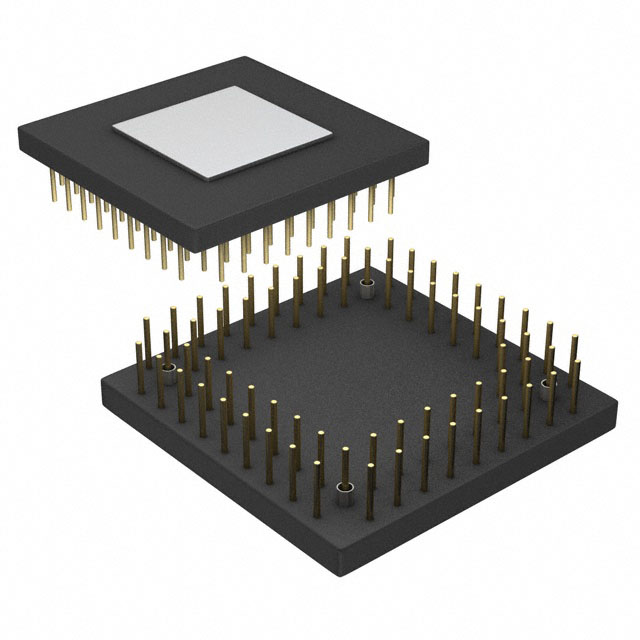

`19 mm * 19 mm (484-ball) or 27 mm * 27 mm (625-ball) PBGA package

`Dual computation blocks-each containing an ALU, a multiplier, a shifter, and a register file

`Dual integer ALUs, providing data addressing and pointer manipulation

`Integrated I/O includes 14-channel DMA controller, external port, four link ports, SDRAM controller, programmable flag pins, two timers, and timer expired pin for system integration

`1149.1 IEEE compliant JTAG test access port for on-chip emulation

`On-chip arbitration for glueless multiprocessing with up to eight TigerSHARC processors on a bus

SpecificationsInternal (Core) Supply Voltage (VDD) 1..............0.3 V to +1.40 V

Analog (PLL) Supply Voltage (VDD_A)1 ............0.3 V to +1.40 V

External (I/O) Supply Voltage (VDD_IO)1 ..........0.3 V to +4.6 V

Input Voltage1 ......................................0.5 V to VDD_IO+0.5 V

Output Voltage Swing1 .........................0.5 V to VDD_IO+0.5 V

Storage Temperature Range1 .........................65ºC to +150ºC

1 Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DescriptionThe ADSP-TS101S TigerSHARC processor is an ultrahigh performance, static superscalar processor optimized for large signal processing tasks and communications infrastructure. The ADSP-TS101S DSP combines very wide memory widths with dual computation blocks-supporting 32- and 40-bit floating-point and 8-, 16-, 32-, and 64-bit fixed-point processing-to set a new standard of performance for digital signal processors. The TigerSHARC processor's static superscalar architecture lets the processor execute up to four instructions each cycle, performing 24 fixedpoint (16-bit) operations or six floating-point operations.

Three independent 128-bit wide internal data buses, each connecting to one of the three 2M bit memory banks, enable quad word data, instruction, and I/O accesses and provide 14.4G bytes per second of internal memory bandwidth. Operating at 300 MHz, the ADSP-TS101S processor's core has a 3.3 ns instruction cycle time. Using its Single-Instruction, Multiple- Data (SIMD) features, the ADSP-TS101S can perform 2.4 billion 40-bit MACs or 600 million 80-bit MACs per second. Table 1 and Table 2 show the DSP's performance benchmarks.

ADSP-TS101S Data Sheet

ADSP-TS101S Data Sheet