Features: • High-speed, low-power, unidirectional, First-In First-Out (FIFO) memories with bus-matching capabilities

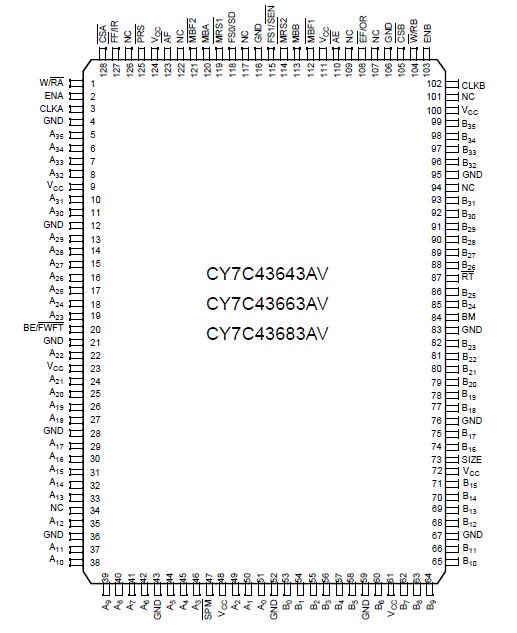

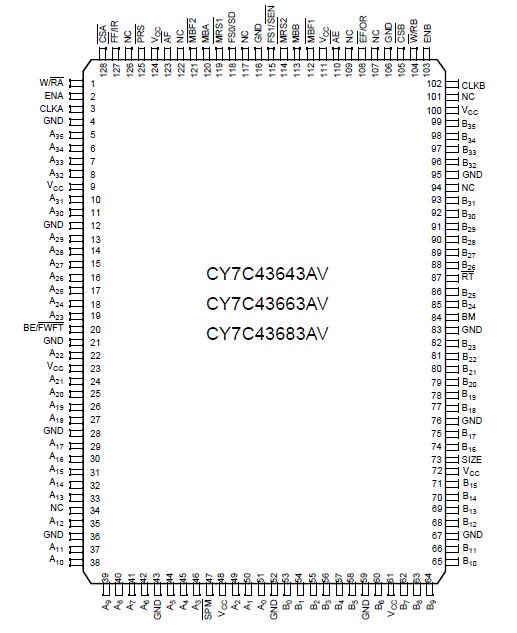

• 1K * 36 (CY7C43643AV)

• 4K * 36 (CY7C43663AV)

• 16K * 36 (CY7C43683AV)

• 0.25-micron CMOS for optimum speed/power

• High-speed 133-MHz operation (7.5-ns Read/Write cycle times)

• Low power

-ICC = 60 mA

-ISB = 10 mA

• FCC ully asynchronous and simultaneous Read and Write operation permitted

• Mailbox bypass register for each FIFO

• Parallel and serial programmable Almost Full and Almost Empty flags

• Retransmit function

• Standard or FWFT user selectable mode

• Partial reset

• Big or Little Endian format for word or byte bus sizes

• 128-pin TQFP packaging

• Easily expandable in width and depthPinout SpecificationsAbove which the useful life may be impaired. For user guidelines,

SpecificationsAbove which the useful life may be impaired. For user guidelines,

not tested.)

Storage Temperature ...................................65°C to +150°C

Ambient Temperature with

Power Applied...............................................55°C to +125°C

Supply Voltage to Ground Potential .................... 0.5V to +7.0V

DC Voltage Applied to Outputs

in High Z State[10].......................................0.5V to VCC+0.5V

DC Input Voltage[10] ...................................0.5V to VCC+0.5V

Output Current into Outputs (LOW)................................... 20 mA

Static Discharge Voltage........................................... ......> 2001V

(per MIL-STD-883, Method 3015)

Latch-Up Current ........................................................ > 200 mADescriptionThe CY7C436X3AV is a monolithic, high-speed, low-power, CMOS Unidirectional Synchronous FIFO memory which supports clock frequencies up to 133 MHz and has Read access times as fast as 6 ns.

The CY7C436X3AV is a synchronous (clocked) FIFO, meaning each port employs a synchronous interface. All data transfers through a port are gated to the LOW-to-HIGH transition of a port clock by enable signals. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple unidirectional interface between microprocessors and/or buses with synchronous control.

Communication between each port may bypass the CY7C436X3AV via two mailbox registers. The mailbox registers' width matches the selected Port B bus width. Each mailbox register has a flag (MBF1 and MBF2) to signal when new mail has been stored. Two kinds of reset are available on the CY7C436X3AV: Master Reset and Partial Reset. Master Reset initializes the Read and Write pointers to the first location of the memory array, configures the FIFO for Big or Little Endian byte arrangement, and selects serial flag programming, parallel flag programming, or one of the three possible default flag offset settings, 8, 16, or 64. The FIFO also has two Master Reset pins, MRS1 and MRS2.

Partial Reset also sets the Read and Write pointers to the first location of the CY7C436X3AV . Unlike Master Reset, any settings existing prior to Partial Reset (i.e., programming method and partial flag default offsets) are retained. Partial Reset is useful since it permits flushing of the FIFO memory without changing any configuration settings. The FIFO has its own independent Partial Reset pin, PRS.

The CY7C436X3AV have two modes of operation: In the CY Standard mode, the first word written to an empty FIFO is deposited into the memory array. A Read operation is required to access that word (along with all other words residing in memory). In the First-Word Fall-Through Mode (FWFT), the first long-word (36-bit-wide) written to an empty FIFO appears automatically on the outputs, no Read operation required (nevertheless, accessing subsequent words does necessitate a formal Read request). The state of the FWFT/STAN pin during FIFO operation determines the mode in use.

The FIFO has a combined Empty/Output Ready flag (EF/OR) and a combined Full/Input Ready flag (FF/IR). The EF and FF functions are selected in the CY Standard mode.EF indicates whether the memory is empty or not. FF indicates whether the memory is full. The IR and OR functions are selected in the First-Word Fall-Through Mode. IR indicates whether or not the FIFO has available memory locations. OR shows whether the FIFO has data available for reading or not. The CY7C436X3AV marks the presence of valid data on the outputs.

The FIFO has a programmable Almost Empty flag (AE) and a programmable Almost Full flag (AF). AE indicates when a selected number of words written to the CY7C436X3AV achieve a predetermined "almost empty state." AF indicates when a selected number of words written to the memory achieve a predetermined "almost full state."[2] FF/IR and AF are synchronized to the port clock that writes data into its array. EF/OR and AE are synchronized to the port clock that reads data from its array. Programmable offset for AE and AF are loaded in parallel using Port A or in serial via the SD input. Three default offset settings are also provided. The AE threshold can be set at 8, 16, or 64 locations from the empty boundary and AF threshold can be set at 8, 16, or 64 locations from the full boundary. All these choices are made using the FS0 and FS1 inputs during Master Reset.

Two or more devices may be used in parallel to create wider data paths.

The CY7C436X3AV are characterized for operation from 0°C 70°C commercial and from 40°C 85°C industrial. Input ESD protection is greater than 2001V, and latch-up is prevented by the use of guard rings.

CY7C43663AV Data Sheet

CY7C43663AV Data Sheet