Features: Access Times of 70, 85, 100ns

Available with Single Chip Selects (EDI88128) or Dual Chip Selects (EDI88130)

2V Data Retention (LP Versions)

CS and OE Functions for Bus Control

TTL Compatible Inputs and Outputs

Fully Static, No Clocks

Organized as 128Kx8

Industrial, Military and Commercial Temperature Ranges

Thru-hole and Surface Mount Packages JEDEC Pinout

*32 pin Ceramic DIP, 0.6 mils wide (Package 9)

*32 lead Ceramic SOJ (Package 140)

Single +5V (±10%) Supply Operation

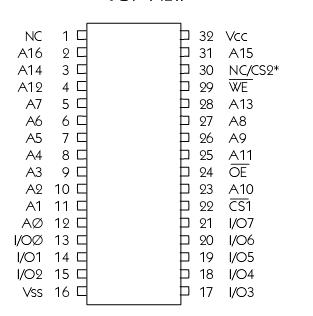

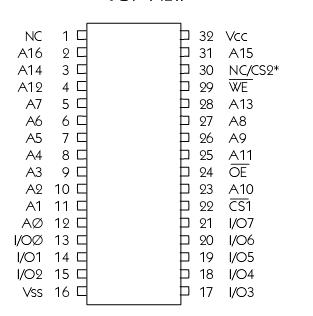

Pinout Specifications

Specifications

| paraneter |

|

unit |

| Voltage on any pin relative to Vss |

-0.5 to 7.0 |

V |

|

operating temperature ta(ambient) Commercial

|

0 to +70 |

°C |

| Industrial |

-40 to +85 |

°C |

| Military |

-55 to +125 |

°C |

| Storage Temperature, Plastic |

-65 to +150 |

°C |

| Power Dissipation |

1 |

W |

| Output Current |

20 |

mA |

| Junction Temperature, TJ |

175 |

°C |

DescriptionThe EDI88128C is a high speed, high performance, Mono-lithic CMOS Static RAM organized as 128Kx8.

The EDI88128C device is also available as EDI88130C with an additional chip select line (CS2) which will automatically power down the device when proper logic levels are applied.

The second chip select line (CS2) can be used to provide system memory security during power down in non-battery backed up systems and simplifiy decoding schemes in memory banking where large multiple pages of memory are required.

The EDI88128C and the EDI88130C have eight bi-directional input-output lines to provide simultaneous access to all bits in a word. An automatic power down feature permits the on-chip circuitry to enter a very low standby mode and be brought back into operation at a speed equal to the address access time.

Low power versions, EDI88128LP and EDI88130LP, offer a 2V data retention function for battery back-up opperation.Military product is available compliant to Appendix A of MIL-PRF-38535.

EDI88128LP70NI Data Sheet

EDI88128LP70NI Data Sheet