Features: • Clock frequency: 183, 166, 143 MHz

• Fully synchronous; all signals referenced to a positive clock edge

• Internal bank for hiding row access/precharge

• Single 3.3V power supply

• LVTTL interface

• Programmable burst length: (1, 2, 4, 8, full page)

• Programmable burst sequence: Sequential/Interleave

• Self refresh modes

• 4096 refresh cycles every 64 ms

• Random column address every clock cycle

• Programmable CAS latency (2, 3 clocks)

• Burst read/write and burst read/single write operations capability

• Burst termination by burst stop and precharge command

• Available in Industrial temperature grade

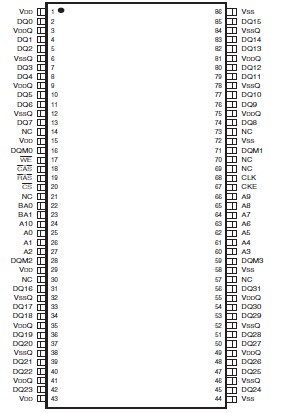

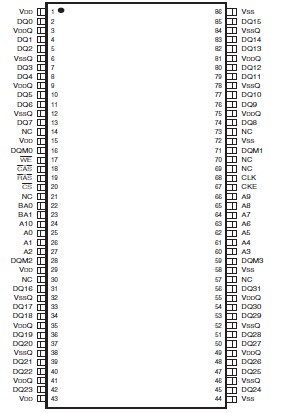

• Available in 400-mil 86-pin TSOP II and 90-ball BGA

• Available in Lead free

Pinout Specifications

Specifications

|

Symbol |

Parameters |

|

Rating |

Unit |

|

VDD MAX |

Maximum Supply Voltage |

|

1.0 to +4.6 |

V |

|

VDDQ

MAX |

Maximum Supply Voltage for Output Buffer |

|

1.0 to +4.6 |

V |

|

VIN |

Input Voltage |

|

1.0 to +4.6 |

V |

|

VOUT |

Output Voltage |

|

1.0 to +4.6 |

V |

|

PD MAX |

Allowable Power Dissipation |

|

1 |

W |

|

I CS |

Output Shorted Current |

|

|

mA |

|

TOPR |

Operating Temperature |

Com

Ind. |

0 to +70

40 to +85 |

°C |

|

TSTG |

Storage Temperature |

|

55 to +150 |

°C |

DescriptionThe 64Mb SDRAM IS42S32200C1 is a high speed CMOS, dynamic random-access memory designed to operate in 3.3Vmemory systems containing 67,108,864 bits. Internally configured as a quad-bank DRAM with a synchronous interface. Each 16,777,216-bit bank is organized as 2,048 rows by 256 columns by 32 bits.

The 64Mb SDRAM IS42S32200C1 includes an AUTO REFRESH MODE, and a power-saving, power-down mode. All signals are registered on the positive edge of the clock signal, CLK. All inputs and outputs are LVTTL compatible.

The 64Mb SDRAM IS42S32200C1 has the ability to synchronously burst data at a high data rate with automatic column-address generation, the ability to interleave between internal banks to hide precharge time and the capability to randomly change column addresses on each clock cycle during burst access.

A self-timed row precharge initiated at the end of the burst sequence is available with the AUTO PRECHARGE function enabled. Precharge one bank while accessing one of the other three banks will hide the precharge cycles and provide seamless, high-speed, random-access operation.

SDRAM IS42S32200C1 read and write accesses are burst oriented starting at a selected location and continuing for a programmed number of locations in a programmed sequence. The registration of an ACTIVE command begins accesses, followed by a READ or WRITE command. The ACTIVE command in conjunction with address bits registered are used to select the bank and row to be accessed (BA0, BA1 select the bank; A0-A10 select the row). The READ or WRITE commands in conjunction with address bits registered are used to select the starting column location for the burst access.

Programmable READ or WRITE burst lengths consist of 1, 2, 4 and 8 locations or full page, with a burst terminate option.

IS42S32200C1 Data Sheet

IS42S32200C1 Data Sheet