Features: • 512 rows × 512 columns × 8 bits × 2

• Fast FIFO (First-In First-Out) Operation: 25 ns cycle time

• Self refresh (No refresh control is required)

• High speed asynchronous serial access Read/Write Cycle Time 25 ns/30 ns/40 ns Access Time 23 ns/30 ns/35 ns

• Variable length delay bit (600 to 262215)

• Write mask function (Output enable control)

• Cascading capability by mode setting

• Single power supply: 3.3 V ±10%

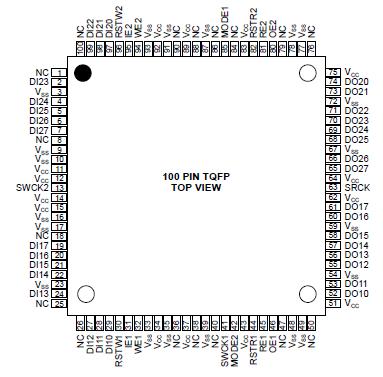

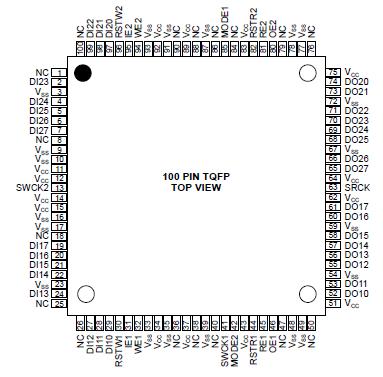

• Package: 100-Pin plastic TQFP (TQFP 100-P-1414-0.50-k) (Product: MS81V04166-xxTB)Pinout Specifications

Specifications

|

Parameter |

Symbol |

Condition |

Rating |

Unit |

| Input Output Voltage |

VT |

at Ta = 25, VSS |

1.0 to +4.5 |

V |

| Output Current |

IOS |

Ta = 25 |

50 |

mA |

| Power Dissipation |

PD |

Ta = 25 |

1 |

W |

| Operating Temperature |

TOPR |

- |

0 to 70 |

|

| Storage Temperature |

TSTG |

- |

-55 to +150 |

|

DescriptionThe MS81V04166 is a single-chip 4Mb FIFO functionally composed of two Oki's 2Mb FIFO (First-In First-Out) memories which were designed for 256k * 8-bit high-speed asynchronous read/write operation. The read clock of each of the 2Mb FIFO memories is connected in common, and the clocks are provided independently of each of the FIFO memories. The MS81V04166 functionally compatible with Oki's 2Mb FIFO memory (MSM51V8222A), can be used as a *16 configuration FIFO.

The MS81V04166 is a field memory for wide or low end use in general commodity TVs and VTRs exclusively and is not designed for high end use in professional graphics systems, which require long term picture storage, data storage, medical use and other storage systems.

The MS81V04166 provides independent control clocks to support asynchronous read and write operations. Different clock rates are also supported, which allow alternate data rates between write and read data streams. The MS81V04166 provides high speed FIFO (First-in First-out) operation without external refreshing: MS81V04166 refreshes its DRAM storage cells automatically, so that it appears fully static to the users. Moreover, fully static type memory cells and decoders for serial access enable the refresh free serial access operation, so that serial read and/or write control clock can be halted high or low for any duration as long as the power is on. Internal conflicts of memory access and refreshing operations are prevented by special arbitration logic.

The MS81V04166's function is simple, and similar to a digital delay device whose delay-bit-length is easily set by reset timing. The delay length and the number of read delay clocks between write and read, is determined by externally controlled write and read reset timings.

MS81V04166's Additional SRAM serial registers, or line buffers for the initial access of 256 * 16-bit enable high speed first-bitaccess with no clock delay just after the write or read reset timings.

The MS81V04166, which is provided with two sets of the serial write clocks, allows the split-screen processing to be implemented easily.

Additionally, the MS81V04166 has a write mask function or input enable function (IE), and read-data skipping function or output enable function (OE). The differences between write enable (WE) and input enable (IE), and etween read enable (RE) and output enable (OE) are that WE and RE can stop serial write/read address increm nts, but IE and OE cannot stop the increment, when write/read clocking is continuously applied to the MS81V04166. The input enable (IE) function allows the user to write into selected locations of the memory only, eaving the rest of the memory contents unchanged. This facilitates data processing to display a "picture in picture"

on a TV screen.

MS81V04166 Data Sheet

MS81V04166 Data Sheet