Features: 32-channel HDLC controller with PCI interface:

• Serial PCM core

Up to 32 independent full-duplex channels

Serial PCM traffic at 2.048, 4.096, 1.544, 1.536,

3.088, 6.176 or 8.192-Mbit/s

• Dynamic Programmable Channel Allocation

Compatible with T1/DS1 24-channel and CEPT 32- channel PCM byte format

Concatenation of any, not necessarily consecutive, time slots to superchannels

independently for receive and transmit direction

Support of H0, H11, H12 ISDN-channels

Subchanneling on each time slot possible

• Bit Processor Functions (adjustable for each channel)

HDLC Protocol

Automatic flag detection

Shared opening and closing flag

Detection of interframe-time-fill change, generation of interframe-time-fill '1's or flags

Zero bit insertion

Flag stuffing and flag adjustment for rate adaption

CRC generation and checking (16 or 32 bits)

Transparent CRC option per channel and/or per message

Error detection (abort, long frame, CRC error, 2 categories of short frames, non-octet frame content)

ABORT/IDLE flag generation

V.110/X.30 Protocol

Automatic synchronization in receive direction, automatic generation of the synchronization pattern in transmit direction

E/S/X bits freely programmable in transmit direction, may be changed during transmission; changes monitored and reported in receive direction

Generation/detection of loss of synchronism

Bit framing with network data rates from 600 bit/s up to 38.4 Kbit/s

Transparent Mode A

Slot synchronous transparent transmission/reception without frame structure

Flag generation, flag stuffing, flag extraction, flag generation

in the abort case with programmable flag

Synchronized data transfer for fractional T1/PRI channels

Transparent Mode B

Transparent transmission/reception in frames delimited by 00H flags

Shared opening and closing flag

Flag stuffing, flag detection, flag generation in the abort case

Error detection (non octet frame content, short frame, long frame)

Transparent Mode R

Transparent transmission/reception with GSM 08.60 frame structure

Automatic 0000H flag generation/detection

Support of 40, 391/2, 401/2 octet frames

Error detection (non octet frame contents, short frame, long frame)

Protocol Independent

Channel inversion (data, flags, IDLE code)

Format conventions as in CCITT Q.921 § 2.8

Data over- and underflow detected

• Microprocessor Interface

32-bit PCI bus interface option, 33 MHz

32-bit De-multiplexed bus interface option, 33 MHz

68 channel DMA controller (64 for 32 serial channels, 4 for 2 LBI channels) with buffer chaining capability

Master 4-DWORD burst read and write capability

Slave single-DWORD read and write capability

Interrupt-circular buffers with variable sizes

Maskable interrupts for each channel

• IOM®-2 Interface with on-chip C/I and monitor handlers

• Synchronous Serial Control (SSC) Interface

• 8-/16-bit Local Bus Interface (LBI)

• General

Connection of up to four MUNICH32X supporting a 128-channel basic access D-channel controller

On-chip Rx and Tx data buffers 256 bytes each

HDLC protocol or transparent mode, support of ECMA 102, CCITT I4.63 RA2, V.110, X.30, DMI mode 0, 1, 2 (bit rate adaption), GSM 08.60 TRAU frames

Loopback mode, complete loop as well as single channel loop

JTAG boundary scan test

0.5 µm low-power CMOS technology

3.3 V and 5 V voltage supply

TTL-compatible inputs/outputs

160-pin P-MQFP package

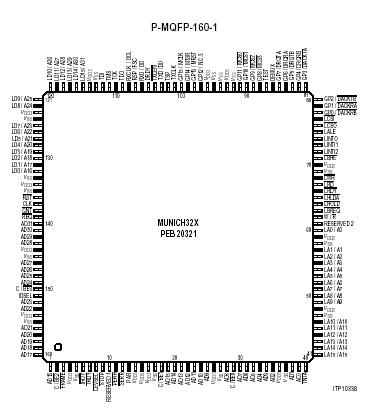

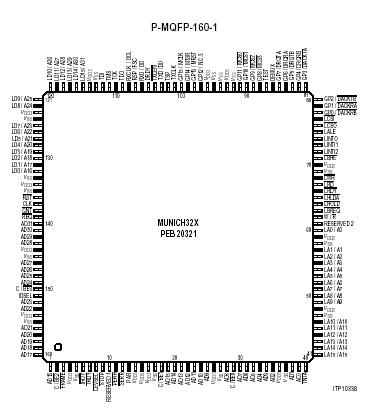

Pinout

PEF20321 Data Sheet

PEF20321 Data Sheet