Features: · Frame alignment/synthesis for PCM30 double frame and CRC-multiframe format.

· Meets CCITT Rec.G704

· Interface to route selectable between HDB3 and fibre optical

· HDB3 outputs switchable between fully bauded and half bauded format

· Error checking via CRC4 procedure

· Insertion and extraction of alarms and facility signals

· Selectable system - clock (4096 kHz/ 8192 kHz)

· Selectable Interface mode (2048/4096 kBit/s) to system internal highway

· Programmable offsets for receive and transmit data

· Two frame receive buffer for receive route clock wander and jitter compensation

· Slip detection and direction indication

· Extended HDB3 error detection

· Error counters for code errors (switchable to "Si zeros counter"), frame errors and CRC4 errors

· Sub-multiframe assigned CRC Error indication with possibility of automatic insertion in Si-bit position of outgoing

multiframe.

· Simplified data transfer between SA9101 and controller, supported by data stacks for receive and transmit signalling data, selectable interruptsources and DMA facilities.

· Double frame marker for serial data extraction support

· Repeated transmission of signalling data, if not updated.

· Three transparent modes for timeslot 0 in transmit direction

· Transparent mode for receive direction

· HDB3 error indication

· Idle channel data insertion selectable for any timeslot

· Channel loopback capabilities, test and diagnostic capabilities

· Parity checks

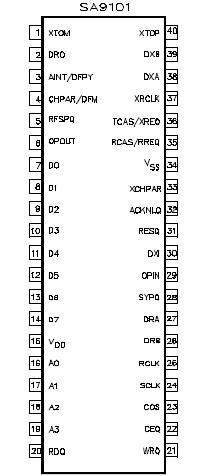

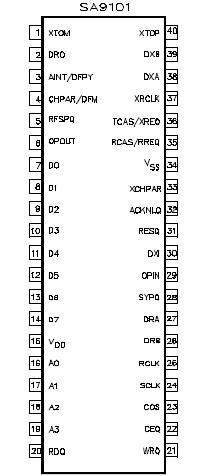

Pinout Specifications

Specifications

| Parameters |

Symbol |

Min |

Max |

Unit |

| Supply Voltage |

VDD- VSS |

-0.3 |

6 |

V |

| Voltage on any I/O pin |

VI/VO |

-0.3 |

VDD+0.3 |

V |

| Current on any I/O pin |

II/IO |

|

20 |

mA |

| Storage Temperature |

TSTG |

-55 |

+125 |

°C |

| Operating Temperature |

TOP |

-10 |

+70 |

°C |

| Package Power Dissipation |

PD |

|

1000 |

mW |

*Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This a stress rating only. Functional operation of the device at these or any other condition above those indicated in the operational sections of this specification, is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

DescriptionThe SA9101 (Frame Alignment unit for PCM30 Systems) is a C-MOS device which implements the interface to PCM30 Transmission Systems.

In the receive direction, the SA9101 performs HDB3 decoding, Frame alignment (selectable between doubleframe and CRC-Multiframe) and extraction of signalling data.

Wander absorption between the PCM carrier and the system internal highway is performed using an internal 2 frame memory. The incoming data stream is monitored status and error conditions of SA9101 are reported through the P interface. In the transmit direction, Frame (and Multiframe) alignment, signalling data insertion and HDB3 coding is performed.

If Multiframe format SA9101 is enabled, CRC4 extraction and checking are carried out in the receive direction and CRC4 data is inserted in the transmit direction.

Stacks for transmit and receive signalling data of SA9101 with DMA capability as well as maskable interrupt sources simplify interfacing to microcontrollers.

Alarm simulation capabilities and selectable channel-loopback, support system diagnostics.

Different transparent modes for timeslot 0 in transmit direction simplify system test and data transmission through the system.

Advanced algorithms for synchronisation of doubleframe and CRC4 multiframe format data, and monitoring of frame and doubleframe formats minimise loss of data.

Control Registers of SA9101 allow different control settings through the P interface.

Advanced C-MOS Technology SA9101 ensures low power consumption and high reliability.

The SA9101 is upwards compatible with the Siemens ACFA (PEB 2035 V4.1) in PCM30 mode.

SA9101 Data Sheet

SA9101 Data Sheet