Features: 1.1 Video decoder

` Six analog inputs, internal analog source selectors, e.g. 6 * CVBS or (2 * Y/C and 2 * CVBS) or (1 * Y/C and 4 * CVBS)

` Two analog preprocessing channels in differential CMOS style for best S/N-performance

` Fully programmable static gain or Automatic Gain Control (AGC) for the selected CVBS or Y/C channel

` Switchable white peak control

` Two built-in analog anti-aliasing filters

` Two 9-bit video CMOS Analog-To-Digital Converters (ADCs), digitized CVBS or Y/C signals are available on the IPD (Image Port Data) port under I2C-bus control

` On-chip clock generator

` Line-locked system clock frequencies

` Digital PLL for horizontal sync processing and clock generation, horizontal and vertical sync detection

` Requires only one crystal (either 24.576 MHz or 32.11 MHz) for all standards

` Automatic detection of 50 and 60 Hz field frequency, and automatic switching between PAL and NTSC standards

` Luminance and chrominance signal processing for PAL BGHI, PAL N, combination PAL N, PAL M, NTSC M, NTSC-Japan, NTSC N, NTSC 4.43 and SECAM

` User programmable luminance peaking or aperture correction

` Cross-colour reduction for NTSC by chrominance comb filtering

` PAL delay line for correcting PAL phase errors

` Brightness Contrast Saturation (BCS) and hue control on-chip

` Two multi functional real-time output pins controlled by I2C-bus

` Multi-standard VBI data slicer decoding World Standard Teletext (WST), North-American Broadcast Text System (NABTS), Closed Caption (CC), Wide Screen Signalling (WSS), Video Programming System (VPS), Vertical Interval Time Code (VITC) variants (EBU/SMPTE) etc.

` Standard ITU 656 Y-CB-CR 4 : 2 : 2 format (8-bit) on IPD output bus

` Enhanced ITU 656 output format on IPD output bus containing:

active video

raw CVBS data for INTERCAST applications (27 MHz data rate)

decoded VBI data

` Detection of copy protected input signals according to the macrovision standard. Can be used to prevent unauthorized recording of pay-TV or video tape signals.

1.2 Video scaler

` Both up and downscaling

` Conversion to square pixel format

` NTSC to 288 lines (video phone)

` Phase accuracy better than 1/64 pixel or line, horizontally or vertically

` Independent scaling definitions for odd and even fields

` Anti-alias filter for horizontal scaling

` Provides output as

scaled active video

raw CVBS data for INTERCAST, WAVE-PHORE, POPCON applications or general VBI data decoding (27 MHz or sample rate converted)

` Local video output for Y-CB-CR 4 : 2 : 2 format (VMI, VIP, ZV).

1.3 Video encoder

` Digital PAL/NTSC encoder with integrated high quality scaler and anti-flicker filter for TV output from a PC

` 27 MHz crystal-stable subcarrier generation

` Maximum graphics pixel clock 45 MHz at double edged clocking, synthesized on-chip or from external source

` Up to 800 * 600 graphics data at 60 Hz or 50 Hz with programmable underscan range

` Three Digital-to-Analog Converters (DACs) at 27 MHz sample rate for CVBS (BLUE, CB), VBS (GREEN, CVBS) and C (RED, CR) (signals in parenthesis are optional); all at 10-bit resolution

` Selectable cross-colour reduction to improve CVBS output

` Non-interlaced CB-Y-CR or RGB input at maximum 4 : 4 : 4 sampling

` Downscaling from 1 : 1 to 1 : 2 and up to 20% upscaling

` Optional interlaced CB-Y-CR input Digital Versatile Disk (DVD)

` Optional non-interlaced RGB output to drive second VGA monitor (bypass mode, maximum 45 MHz)

` 3 * 256 bytes RGB Look-Up Table (LUT)

` Support for hardware cursor

` Programmable border colour of underscan area

` On-chip 27 MHz crystal oscillator (3rd-harmonic or fundamental 27 MHz crystal)

` Encoder can be master or slave

` Programmable horizontal and vertical input synchronization phase

` Programmable horizontal sync output phase

` Internal Colour Bar Generator (CBG)

` Optional support of various VBI data insertion as

WST-625, WSS, VPS

WST-525, NABTS

Closed Caption, Copy Generation Management System (CGMS)

` Macrovision Pay-per-View copy protection system rev. 7.01 and rev. 6.1 as option; this applies to SAA7108E only. The device is protected by USA patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. Use of the Macrovision anti-copy process in the device is licensed for non-commercial home use only. Reverse engineering or disassembly is prohibited. Please contact your nearest Philips Semiconductors sales office for more

information.

1.4 Common features

` 5 V tolerant digital I/O ports

` I2C-bus controlled (full read-back ability by an external controller, bit rate up to 400 kbits/s)

` Versatile power-save modes

` Boundary scan test circuit complies with the "IEEE Std. 1149.b1-1994" (separate ID codes for decoder and encoder)

` Monolithic CMOS 3.3 V device

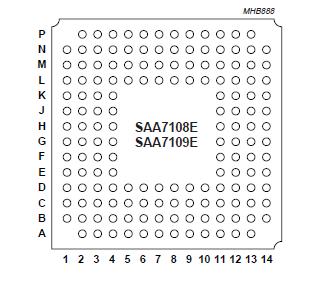

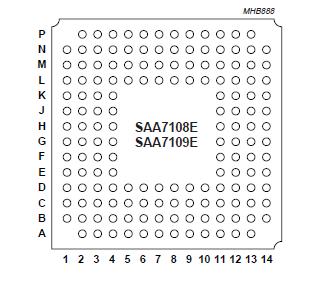

` BGA156 package

` Moisture Sensitive Level (MSL): e3.

Application· Notebook (low-power consumption)

· PCMCIA card application

· AGP based graphics cards

· PC editing

· Image processing

· Video phone applications

· INTERCAST and PC teletext applications

· Security applications

· Hybrid satellite set-top boxes.Pinout Specifications

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

MAX. |

UNIT |

| VDDD |

digital supply voltage |

|

-0.5 |

+4.6 |

V |

| VDDA |

analog supply voltage |

|

-0.5 |

+4.6 |

V |

| Vi(A) |

input voltage at analog inputs |

|

-0.5 |

+4.6 |

V |

| Vi(n) |

input voltage at pins XTALI, SDA and SCL |

|

-0.5 |

VDDD + 0.5 |

V |

| Vi(D) |

input voltage at digital inputs or I/O pins |

outputs in 3-state |

-0.5 |

+4.6 |

V |

outputs in 3-state;

note 1 |

-0.5 |

+5.5 |

V |

| VSS |

voltage difference between VSSA(n) and VSSD(n) |

|

- |

100 |

mV |

| Tstg |

storage temperature |

|

-65 |

+150 |

°C |

| Tamb |

ambient temperature |

|

0 |

70 |

°C |

| Vesd |

electrostatic discharge voltage |

human body model;

note 2 |

- |

±2000 |

V |

machine model;

note 3 |

- |

±150 |

V |

DescriptionThe SAA7108E; SAA7109E is a new multi-standard video decoder and encoder chip, offering high quality video input and TV output processing as required by PC-99 specifications. SAA7108E; SAA7109E enable hardware manufacturers to implement versatile video functions on a significantly reduced printed-circuit board area at very competitive costs.

Separate pins of SAA7108E; SAA7109E for supply voltages as well as for I2C-bus control and boundary scan test have been provided for the video encoder and decoder sections to ensure both flexible handling and optimized noise behaviour.

The video encoder of SAA7108E; SAA7109E is used to encode PC graphics data at maximum 800 × 600 resolution to PAL (50 Hz) or NTSC (60 Hz) video signals. A programmable scaler and interlacer ensures properly sized and flicker-free TV display as CVBS or S-video output.

Alternatively, the three Digital-to-Analog Converters (DACs)of SAA7108E; SAA7109E can output RGB signals together with a TTL composite sync to feed SCART connectors.

When the scaler/interlacer is bypassed, a second VGA monitor can be connected to the RGB outputs and separate H and V-syncs as well, thereby serving as an auxiliary monitor at maximum 800 ´ 600 resolution/60 Hz (PIXCLK < 45 MHz).

The video decoder, a 9-bit video input processor, is a combination of a 2-channel analog pre-processing circuit including source selection, anti-aliasing filter and Analog-to-Digital Converter (ADC), automatic clamp and gain control, a Clock Generation Circuit (CGC), and a digital multi-standard decoder (PAL BGHI, PAL M, PAL N, combination PAL N, NTSC M, NTSC-Japan, NTSC N, NTSC 4.43 and SECAM).

The decoder of SAA7108E; SAA7109E includes a brightness, contrast and saturation control circuit, a multi-standard VBI data slicer and a 27 MHz VBI data bypass. The pure 3.3 V (5 V compatible) CMOS circuit SAA7108E; SAA7109E, consisting of an analog front-end and digital video decoder, a digital video encoder and analog back-end, is a highly integrated circuit especially designed for desktop video applications.

The decoder of SAA7108E; SAA7109E is based on the principle of line-locked clock decoding and is able to decode the colour of PAL, SECAM and NTSC signals into ITU-R BT.601 compatible colour component values.

The encoder of SAA7108E; SAA7109E can operate fully independently at its own variable pixel clock, transporting graphics input data, and at the line-locked, single crystal-stable video encoding clock.

As an option, it is possible to slave the video PAL/NTSC encoding to the video decoder clock with the encoder FIFO acting as a buffer to decouple the line-locked decoder clock from the crystal-stable encoder clock.

SAA7108E Data Sheet

SAA7108E Data Sheet