Features: 1.1 Video acquisition/clock

` Up to sixteen analog CVBS, split as desired (all of the CVBS inputs optionally can be used to convert e.g. Vestigial Side Band (VSB) signals)

` Up to eight analog Y + C inputs, split as desired

` Up to four analog component inputs, with embedded or separate sync, split as desired

` Four on-chip anti-aliasing filters in front of the Analog-to-Digital Converters (ADCs)

` Automatic Clamp Control (ACC) for CVBS, Y and C (or VSB) and component signals

` Switchable white peak control

` Four 9-bit low noise CMOS ADCs running at twice the oversampling rate (27 MHz)

` Fully programmable static gain or Automatic Gain Control (AGC), matching to the particular signal properties

` On-chip line-locked clock generation in accordance with "ITU 601"

` Requires only one crystal (32.11 or 24.576 MHz) for all standards

` Horizontal and vertical sync detection.

1.2 Video decoder

` Digital PLL for synchronization and clock generation from all standards and non-standard video sources e.g. consumer grade VTR

` Automatic detection of any supported colour standard

` Luminance and chrominance signal processing for PAL B, G, D, H, I and N, combination PAL N, PAL M, NTSC M, NTSC-Japan, NTSC 4.43 and SECAM

` Adaptive 2/4-line comb filter for two dimensional chrominance/luminance separation, also with VTR signals

Increased luminance and chrominance bandwidth for all PAL and NTSC standards

Reduced cross colour and cross luminance artefacts

` PAL delay line for correcting PAL phase errors

` Brightness Contrast Saturation (BCS) adjustment, separately for composite and baseband signals

` User programmable sharpness control

` Detection of copy-protected signals according to the macrovision standard, indicating level of protection

` Independent gain and offset adjustment for raw data path.

1.3 Component video processing

` RGB component inputs

` Y-PB-PR component inputs

` Fast blanking between CVBS and synchronous component inputs

` Digital RGB to Y-CB-CR matrix.

1.4 Video scaler

` Horizontal and vertical downscaling and upscaling to randomly sized windows

` Horizontal and vertical scaling range: variable zoom to 1/64 (icon) (note: H and V zoom are restricted by the transfer data rates)

` Anti-alias and accumulating filter for horizontal scaling

` Vertical scaling with linear phase interpolation and accumulating filter for anti-aliasing (6-bit phase accuracy)

` Horizontal phase correct up and downscaling for improved signal quality of scaled data, especially for compression and video phone applications, with 6-bit phase accuracy (1.2 ns step width)

` Two independent programming sets for scaler part, to define two 'ranges' per field or sequences over frames

` Fieldwise switching between decoder part and expansion port (X-port) input

` Brightness, contrast and saturation controls for scaled outputs.

1.5 Vertical Blanking Interval (VBI) data decoder and slicer

` Versatile VBI-data decoder, slicer, clock regeneration and byte synchronization e.g. for World Standard Teletext (WST), North-American Broadcast Text System (NABTS), close caption, Wide Screen Signalling (WSS) etc.

1.6 Audio clock generation

` Generation of a field-locked audio master clock to support a constant number of audio clocks per video field

` Generation of an audio serial and left/right (channel) clock signal.

1.7 Digital I/O interfaces

` Real-time signal port (R port), inclusive continuous line-locked reference clock and real-time status information supporting RTC level 3.1 (refer to document "RTC Functional Specification" for details)

` Bidirectional expansion port (X-port) with half duplex functionality (D1), 8-bit Y-CB-CR

Output from decoder part, real-time and unscaled

Input to scaler part, e.g. video from MPEG decoder (extension to 16-bit possible)

` Video image port (I-port) configurable for 8-bit data (extension to 16-bit possible) in master mode (own clock), or slave mode (external clock), with auxiliary timing and handshake signals

` Discontinuous data streams supported

` 32-word * 4-byte FIFO register for video output data

` 28-word * 4-byte FIFO register for decoded VBI-data output

` Scaled 4 : 2 : 2, 4 : 1 : 1, 4 : 2 : 0, 4 : 1 : 0 Y-CB-CR output

` Scaled 8-bit luminance only and raw CVBS data output

` Sliced, decoded VBI-data output.

1.8 Miscellaneous

` Power-on control

` 5 V tolerant digital inputs and I/O ports

` Software controlled power saving standby modes supported

` Programming via serial I2C-bus, full read back ability by an external controller, bit rate up to 400 kbits/s

` Boundary scan test circuit complies with the "IEEE Std. 1149.b1 - 1994".

Application· PC-video capture and editing

· Personal video recorders (time shifting)

· Cable, terrestrial, and satellite set-top boxes

· Internet terminals

· Flat-panel monitors

· DVD-recordable players

· AV-ready hard-disk drivers

· Digital televisions/scan conversion

· Video surveillance/security

· Video editing/post production

· Video phones

· Video projectors

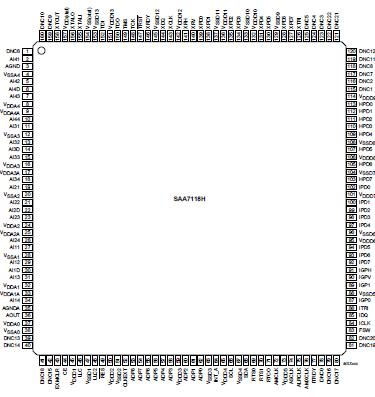

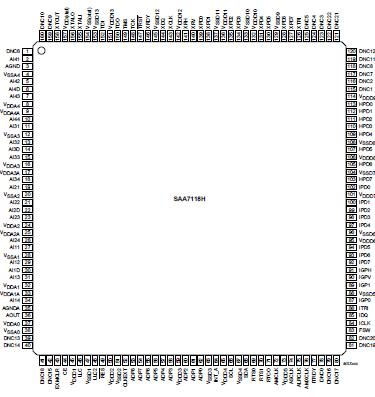

· Digital VCRs.Pinout Specifications

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

MAX. |

UNIT |

| VDDD |

digital supply voltage |

|

-0.5 |

+4.6 |

V |

| VDDA |

analog supply voltage |

|

-0.5 |

+4.6 |

V |

| VIA |

input voltage at analog inputs |

|

-0.5 |

VDDA + 0.5(1) |

V |

| VOA |

output voltage at analog output |

|

-0.5 |

VDDA + 0.5 |

V |

| VID |

input voltage at digital inputs and outputs |

outputs in 3-state;

note 2 |

-0.5 |

+5.5 |

V |

| VOD |

output voltage at digital outputs |

outputs active |

-0.5 |

VDDD + 0.5 |

V |

| VSS |

voltage difference between VSSAn and VSSDn |

|

- |

100 |

mV |

| Tstg |

storage temperature |

|

-65 |

+150 |

°C |

| Tamb |

ambient temperature |

|

0 |

70 |

°C |

| Vesd |

electrostatic discharge all pins |

note 3 |

-2000 |

+2000 |

V |

Notes

1. Maximum 4.6 V.

2. Except pin XTALI.

3. Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k resistor.DescriptionThe SAA7118 is a video capture device for applications at the image port of VGA controllers.

Philips X-VIP SAA7118 is a new multistandard comb filter video decoder chip with additional component processing, providing high quality, optionally scaled, video.

The SAA7118 is a combination of a four-channel analog preprocessing circuit including source selection, anti-aliasing filter and ADC with succeeding decimation filters from 27 to 13.5 MHz data rate. Each preprocessing channel comes with an automatic clamp and gain control. The SAA7118 combines a Clock Generation Circuit (CGC), a digital multistandard decoder containing two-dimensional chrominance/luminance separation by an adaptive comb filter and a high performance scaler, including variable horizontal and vertical up and downscaling and a brightness, contrast and saturation control circuit.

SAA7118 Data Sheet

SAA7118 Data Sheet