Features: EPICTM (Enhanced-Performance Implanted CMOS) Submicron Process

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

Latch-Up Performance Exceeds 250 mA Per JESD 17

Typical VOLP (Output Ground Bounce)< 0.8 V at VCC = 3.3 V, TA = 25°C

Typical VOHV (Output VOH Undershoot)> 2 V at VCC = 3.3 V, TA = 25°C

Inputs Accept Voltages to 5.5 V

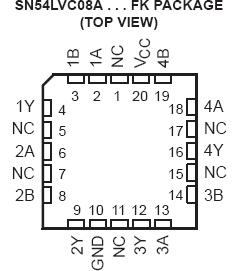

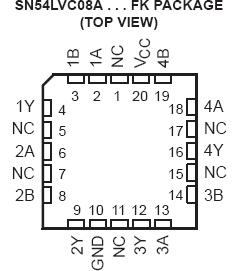

Package Options Include Plastic Small-Outline (D), Shrink Small-Outline (DB), and Thin Shrink Small-Outline (PW) Packages, Ceramic Chip Carriers (FK) and Flat (W) Packages, and DIPs (J)

Pinout Specifications

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 6.5 V

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 6.5 V

Output voltage range, VO (see Notes 1 and 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....0.5 V to VCC + 0.5 V

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 mA

Continuous output current, IO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±50 mA

Continuous current through VCC or GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....±100 mA

Package thermal impedance, qJA (see Note 3): D package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .......127°C/W

DB package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .........158°C/W

PW package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ........170°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65°C to 150°C

DescriptionThe SN54LVC08A quadruple 2-input positive-AND gate is designed for 2.7-V to 3.6-V VCC operation and the SN74LVC08A quadruple 2-input positive-AND gate is designed for 1.65-V to 3.6-V VCC operation.

The SN54LVC08A devices perform the Boolean function Y = A • B or Y=A+B in positive logic.

Inputs of SN54LVC08A can be driven from either 3.3-V or 5-V devices. This feature allows the use of these devices as translators in a mixed 3.3-V/5-V system environment.

The SN54LVC08A is characterized for operation over the full military temperature range of 55°C to 125°C. The SN74LVC08A is characterized for operation from 40°C to 85°C.

SN54LVC08A Data Sheet

SN54LVC08A Data Sheet