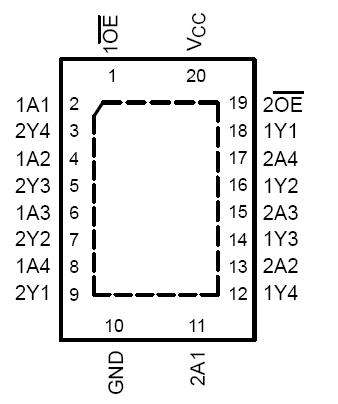

SN74AUCH240: Features: ` Optimized for 1.8-V Operation and is 3.6-V I/O Tolerant to Support Mixed-Mode Signal Operation` Ioff Supports Partial-Power-Down Mode Operation` Sub 1-V Operable` Max tpd of 1.7 ns at 1....

floor Price/Ceiling Price

- Part Number:

- SN74AUCH240

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

SN74AUCH240 Data Sheet

SN74AUCH240 Data Sheet