Manufacturer: Texas Instruments

Number of Circuits: 1

Operating Temperature: -40°C ~ 85°C

Mounting Type: Surface Mount

Packaging: Tape & Reel (TR)Alternate Packaging

Number of Inputs: 2

Features: -

Logic Type: OR Gate

Series: 74AUP

Current - Quiescent (Max): 0.5µA

Current - Output High, Low: 4mA, 4mA

Voltage - Supply: 0.8 V ~ 3.6 V

Logic Level - Low: 0.7 V ~ 0.9 V

Logic Level - High: 1.6 V ~ 2 V

Max Propagation Delay @ V, Max CL: 6.4ns @ 3V ~ 3.6V, 30pF

Supplier Device Package: 5-DSBGA, 5-WCSP (1.4x0.9)

Package / Case: 5-XFBGA, WLCSP

Features: ` Available in the Texas Instruments

NanoStar and NanoFree Packages

` Low Static-Power Consumption; ICC = 0.9-A Max

` Low Dynamic-Power Consumption; Cpd = 4.3 pF Typ at 3.3 V

` Low Input Capacitance; Ci = 1.5 pF Typ

` Low Noise − Overshoot and Undershoot <10% of VCC

` Ioff Supports Partial-Power-Down Mode Operation

` Input Hysteresis Allows Slow Input

Transition and Better Switching Noise

Immunity at the Input

(Vhys = 250 mV Typ at 3.3 V)

` Wide Operating VCC Range of 0.8 V to 3.6 V

` Optimized for 3.3-V Operation

` 3.6-V I/O Tolerant to Support Mixed-Mode

Signal Operation

` tpd = 4.6 ns Max at 3.3 V

` Suitable for Point-to-Point Applications

` Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class II

` ESD Performance Tested Per JESD 22

− 2000-V Human-Body Model

(A114-B, Class II)

− 200-V Machine Model (A115-A)

− 1000-V Charged-Device Model (C101)

` ESD Protection Exceeds ±5000 V With

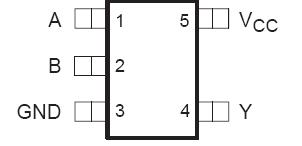

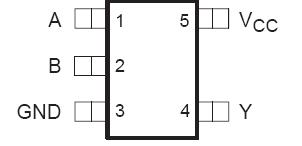

Human-Body ModelPinout SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 4.6 V

SpecificationsSupply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 4.6 V

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−0.5 V to 4.6 V

Voltage range applied to any output in the high-impedance or power-off state, VO

(see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 4.6 V

Output voltage range in the high or low state, VO (see Note 1) . . . . . . . . . . . . . . . . . . .−0.5 V to VCC + 0.5 V

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−50 mA

Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −50 mA

Continuous output current, IO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±20 mA

Continuous current through VCC or GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±50 mA

Package thermal impedance, JA (see Note 2): DBV package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206°C/W

DCK package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252°C/W

DRL package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142°C/W

YEP/YZP package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .−65°C to 150°C

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51-7.DescriptionThe AUP family is TI's premier solution to the industry's low-power needs in battery-powered portable applications. This SN74AUP1G32YEPR family ensures a very low static and dynamic power consumption across the entire VCC range of 0.8 V to 3.6 V, resulting in increased battery life. This product also maintains excellent signal integrity (see Figures 1 and 2).

This SN74AUP1G32YEPR single 2-input positive-OR gate performs the Boolean function Y � A�B or Y � A • B in positive logic. NanoStar and NanoFree package technology is a major breakthrough in IC packaging concepts, using the die as the package.

This SN74AUP1G32YEPR device is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

Parameters: | Technical/Catalog Information | SN74AUP1G32YEPR |

| Vendor | Texas Instruments |

| Category | Integrated Circuits (ICs) |

| Number of Circuits | 1 - Single |

| Package / Case | 5-DSBGA |

| Logic Type | OR Gate |

| Packaging | Tape & Reel (TR) |

| Mounting Type | Surface Mount |

| Number of Inputs | 2 |

| Current - Output High, Low | 4mA, 4mA |

| Supply Voltage | 0.8 V ~ 3.6 V |

| Operating Temperature | -40°C ~ 85°C |

| Voltage - Supply | 0.8 V ~ 3.6 V |

| Drawing Number | * |

| Lead Free Status | Lead Free |

| RoHS Status | RoHS Compliant |

| Other Names | SN74AUP1G32YEPR

SN74AUP1G32YEPR

|

SN74AUP1G32YEPR Data Sheet

SN74AUP1G32YEPR Data Sheet