Features: 3.3V and 5V power supply options

1.12GHz maximum VCO frequency

30MHz to 560MHz reference input operating frequency

External 2.0GHz VCO capability

Frequency doubler mode

Low jitter differential design

PECL differential outputs

External loop filter optimizes performance/cost

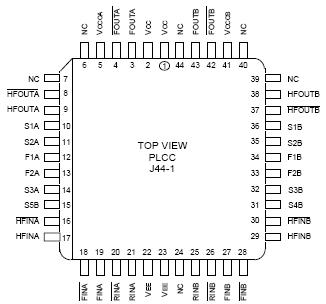

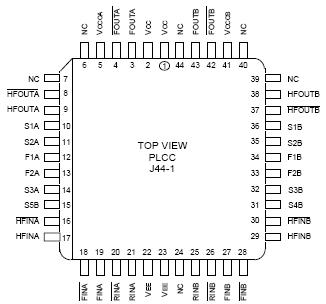

Available in 44-pin PLCC packageApplication Workstations

Advanced communications

High-performance computingPinout Specifications

Specifications

| Symbol |

Parameter |

Value |

Unit |

| VCC |

Power Supply Voltage |

0.5 to +7.0 |

V |

| VI |

TTL Input Voltage |

0.5 to VCC |

V |

| II |

TTL Input Current |

30 to +5.0 |

mA |

| IOUT |

ECL Output Current

- Continuous

- Surge |

50

100 |

mA |

| Tstore |

Storage Temperature |

65 to +150 |

°C |

| TA |

Operating Temperature Range(3) |

0 to +85 |

°C |

3. All DC and AC electrical characteristics are specified over the operating temperature range.DescriptionThe SY89423V device consists of two identical, low jitter, digital Phase Locked Loops based on Micrel-Synergy's differential PLL technology. Each PLL is capable of operating in the 30MHz to 560MHz reference input frequency range, and is independent of the other, and is configurable separately. The SY89423V PLLs can be configured to be matched in all regards, or can be configured so that PLLB is used as a frequency doubler, while PLLA is used to regenerate the undoubled frequency. Each PLL is capable of operating up to 2000MHz with the HFIN input and an external VCO.

Two reference inputs (RINX and RINX), two feedback inputs (FINX and FINX), two high frequency inputs (HFINX and HFINX), two filter pins (F1X and F2X), two normal outputs (FOUTX and FOUTX), and two high frequency outputs (HFOUTX and HFOUTX) are provided for each of the two PLLs. The reference, feedback, and high frequency inputs can be used as either differential or single-ended inputs. External reference voltage generators are required for single-ended drive.Feedback for the loops is realized by connecting FOUTX, FOUTX to FINX, FINX by means of external circuitry. This allows the user the flexibility of inserting additional circuitry off-chip in the feedback paths, such as an additional divider. Pulldown resistors are required for the FOUTX and FOUTX pins, and for the HFOUTX and HFOUTX pins. Use of a phase-frequency detector in each SY89423V PLL results in excellent locking and tracking characteristics. Error correction voltages are generated by the detector if either phase or frequency deviations occur. The VCO in each PLL has a frequency range covering more than a 2:1 ratio from 480MHz to 1120MHz.

Select pins S1A, S2A, S1B, S2B, and S3B are used to program the N dividers for optimum VCO operation, in other words with the VCO operating in the center of its range. When both S3B and S5B are low, PLLB is identical to PLLA. When S5B is high, the 2X frequency multiplication option is enabled. Select pins S3A and S4B enable the HF inputs for PLLA and PLLB respectively, which allows the use of an external VCO in either PLL. All the select pins of SY89423V are TTL inputs.

SY89423V Data Sheet

SY89423V Data Sheet