Features: Overall Features

• Standalone PCI to ATA host controller chip

• Compliant with PCI Specification, revision 2.2.

• Compliant with PCI IDE Controller Specification, revision 1.0.

• Compliant with Programming Interface for Bus Master IDE Controller, revision 1.0.

• Compliant with ATA/ATAPI-6 specifications.

• Compliant with UDMA6 ATA/133 Specification

• Driver support for Win98, WinME, NT4, Win2K and XP.(IDE and RAID including Linux IDE support)

• Supports up to 4Mbit external FLASH or EPROM for BIOS expansion.

• Supports an external EEPROM, FLASH or serial EPROM for programmable subsystem vendor ID and subsystem product ID.

• Supports all necessary test requirements for WHQL.

• Supports the Microsoft driver protocols for PIO and bus master DMA operations.

• Supports DMA transfers across the 64K physical boundary and supports transfer sizes >64K (up to 2TB)

• Provides virtual DMA support for efficient PCI bus utilization for PIO transfers

• Fabricated in a 0.35 CMOS process with a 3.3 volt core and 5 volt tolerant I/Os.

• Available in a 144-pin LQFP package

PCI Features

• Supports PCI 33 MHz with 32-bit data.

• Supports PCI PERR and SERR reporting.

• Supports PCI bus master operations: Memory Read, Memory Read Multiple, and Memory Write.

• Supports PCI bus target operations: Configuration Read, Configuration Write, I/O Read, I/O Write, Memory

Read, Memory Write, Memory Read Line (Memory Read), Memory Read Multiple (Memory Read), Memory

Write and Invalidate (Memory Write).

• Supports byte alignment for odd-byte PCI address access.

• Supports jumper configurable PCI class code.

• Supports programmable and EEPROM, FLASH and EPROM loadable PCI class code.

ATA Features

• Supports two independent ATA channels.

• Supports ATA 133.

• Supports full speed burst transfers on the ATA bus.

• Supports software-controlled ATA bus tri-state.

• Supports device specific timing registers.

• Supports device read-ahead and write-ahead capability under Virtual DMA.

Other Features

• Features one 256-byte FIFO (32-bit x 64 deep) per IDE channel for host reads and writes.

• Features ATA to PCI interrupt masking.

• Features command buffering from the PCI to ATA.

• Features Virtual DMA: Bus master transfer on the PCI bus and PIO transfer on the ATA bus.

• Features Watch Dog Timer for fault resiliency.

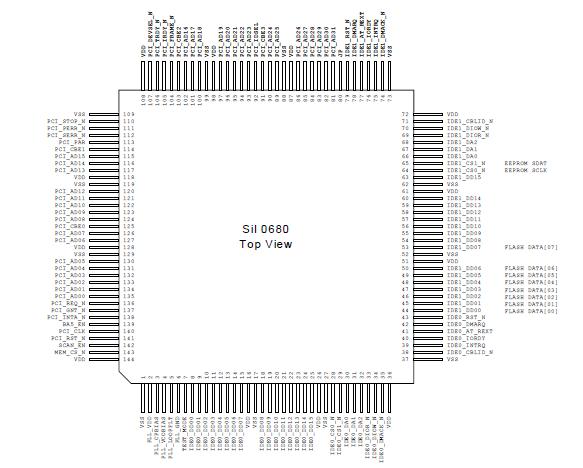

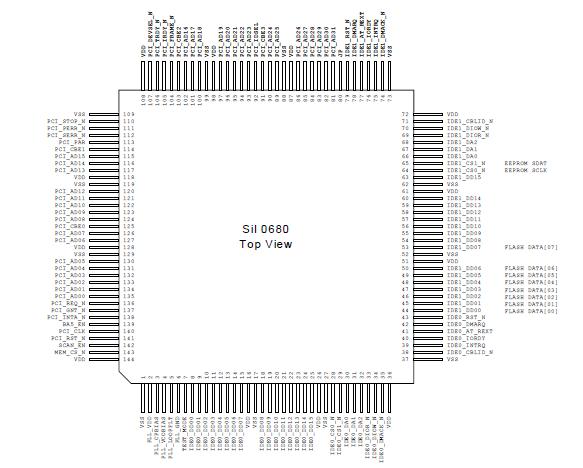

Pinout Specifications

Specifications

|

Symbol |

Parameter |

Condition |

Type |

Limits |

Unit |

|

Min |

Typ |

Max |

|

VDD |

Supply Voltage |

- |

- |

3.0 |

3.3 |

3.6 |

V |

|

IDD |

Supply Current

(See Sec. 2.5) |

Quiescent |

- |

- |

250 |

- |

mA |

|

Operating |

- |

- |

350 |

- |

|

VIH |

Input High Voltage |

- |

3.3V PCI |

0.5xVDD |

- |

- |

V |

|

- |

Non-PCI |

2.0 |

- |

- |

|

VIL |

Input Low Voltage |

- |

3.3V PCI |

- |

- |

0.3xVDD |

V |

|

- |

Non-PCI |

- |

- |

0.8 |

|

V+ |

Input High Voltage |

- |

Schmitt |

- |

1.8 |

2.3 |

V |

|

V- |

Input Low Voltage |

- |

Schmitt |

0.5 |

0.9 |

- |

V |

|

VH |

Hysteresis Voltage |

- |

Schmitt |

0.4 |

- |

- |

V |

|

IIH |

Input High Current |

VIN = VDD |

- |

-10 |

- |

10 |

A |

|

IIL |

Input Low Current |

VIN = VSS |

- |

-10 |

- |

10 |

A |

|

VOH |

Output High

Voltage |

- |

- |

2.4 |

- |

- |

V |

|

VOL |

Output Low Voltage |

- |

- |

- |

- |

0.4 |

V |

|

IOZ |

3-State Leakage

Current |

- |

- |

-10 |

- |

10 |

A |

DescriptionThe PCI-680A is available in a 144-pin LQFP (Thin Quad Flat Package) including more ground pins in order to accommodate the new higher data transfer rate specified in the ATA/ATAPI-6 specification. The chip has an internal

phase lock loop that will provide the 100/133MHz (selectable) internal clock, allowing a data transfer rate of 100/133MB/sec (selectable) on ATA interface. A built-in 80-pin cable detector provides users the ability to determine

whether a cable can support the latest Ultra ATA/100/133 (selectable) transfer rate. The PCI-680 is capable of supporting Native mode, external BIOS, Enhanced IDE mode (ultra DMA and multiword DMA mode) and PIO mode.

SiI0680A Data Sheet

SiI0680A Data Sheet