Features: • Supports Distributed Arbitration for Futurebus+ Master Selection

• Supports Arbitrated Messages In Distributed and Central Modes

• Enables Use of a Common Hardware and Software Interface for Both Distributed and Central Modes

• Requires No Hardware Modifications for Changing Between Distributed and Central Modes

• Provides a CSR Bus Interface for Easy

Integration into the Futurebus+ CSR Address Space

• Has Two Bus Request Lines That Each May Be Assigned Any One of 256 Priority Levels

• Supports Round-Robin Fairness Arbitration

Within Two Separate Priority Levels to Avoid Starvation of Any Single Module

• Supports Distributed-Mode Bus Parking to Improve Performance of Successive Bus

Acquisitions By a Single Module During

Idle-Bus Conditions

• Offers Accurate Arbitration Settling TIme and Glitch-Filter Programmability to Allow Optimal Arbitration Bus Performance

• Provides FIFO for Capturing up to Four Incoming Arbitrated Messages

• Provides Hardware Support of TargetedInterrupts

• Supports Power-Fail Message Indication With a Separate Terminal and Interrupt

• Provides On-Chip Error Time-Out Detection

• Has a JTAG Test Port

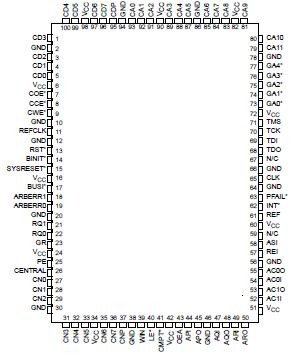

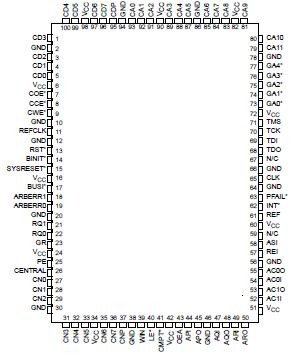

• Package is a Ceramic Quad Flat Package Lead Pitch Is 0.5 mm (19.7 mil)Pinout Description

DescriptionThe TFB2010M arbitration bus controller (ABC) is a member of the Texas Instruments Futurebus+ chip set. This chip set provides an integrated approach to the Futurebus+ interface that reduces new-product design time, allows more functionality per circuit board, improves overall interface reliability, and reduces end-user down time through built-in test capabilities. The Futurebus+ chip set is capable of supporting, in any combination, 32- or 64-bit data widths on both the host-bus interface (HIF) and Futurebus+. The address width is programmable to be 32-bits or 36-bits (with either data width).

The TFB2010M performs the Futurebus+ distributed arbitration protocol to gain tenure of the bus (distributed mode only), to send and receive arbitrated messages (central or distributed mode), and to update central-mode arbiter priorities (central mode only).

The TFB2010M can be used in conjunction with a central-bus arbiter as an arbitrated-message controller to program the central-bus arbiter, send asynchronous interrupts, or send event messages or interrupts to other modules. In the case of a failure in the central-bus arbiter or if distributed arbitration is desired, it can be used as a distributed-arbitration controller without a change in the host software. Priority changes are sent to the central arbiter as arbitrated messages. This device monitors the bus for arbitration messages, storing these in a FIFO or in the targeted-interrupt register for reference by the processor. It also provides the necessary control functions to gain control of the Futurebus+ for a module attempting to perform a bus transaction when operating in the distributed-arbitration mode.

Initialization, interrupt handling, and control of this device are handled through the CSR registers. All registers are memory mapped into the Futurebus+ CSR space and made accessible to a module-processing element through the CSR interface.

Priority numbers ranging from 0 to 255 are independently maintained for RQ<0> and RQ<1> in two CSR registers. A third register is used to send any desired arbitrated message. Priority and send arbitration-message (SAM) registers may be modified at any time via the CSR bus. A newly modified arbitration number, request level (RQ1), or mode of operation is not used by a module until the idle state is observed.

Time-out error checkers are provided for phases 1, 2, 4 and for phase 0 between the first and second pass of a two-pass arbitration cycle. Phases 2 and 4 are hardwired to a time out of between 1 and 2 s. Programmable wired-OR glitch filters are provided for the handshake lines and the RE input.

TFB2010M Data Sheet

TFB2010M Data Sheet