Features: ` Full compliance with the Universal Serial Bus Specification Revision 1.1.

` Backward compatible with USS-820B, USS-820C, and USS-820D revisions.

` Self-powered or bus-powered USB device. Meets USB power specifications for bus-powered devices.

` Full-speed USB device (12 Mbits/s).

` USB device controller with protocol control and administration for up to 16 USB endpoints.

` Supports control, interrupt, bulk, and isochronous transfers for all 16 endpoints.

` Programmable endpoint types, FIFO sizes, and internal 1120-byte logical (2240-byte physical for dual-packet mode) shared FIFO storage allow a wide variety of configurations.

` Dual-packet mode of FIFOs reduces latency.

` Supports USB remote wake-up feature.

` On-chip crystal oscillator allows external 12 MHz crystal or 3 V/5 V clock source.

` On-chip analog PLL creates 48 MHz clock from internal 12 MHz clock.

` Integrated USB transceivers.

` 5 V tolerant I/O buffers allow operation in 3 V or 5 V system environments for 0 °C to 70 °C temperature range.

` 5 V tolerant I/O buffers allow operation in 3 V only system environments for 20 °C to +85 °C temperature range.

` Implemented in Agere Systems Inc. 0.25 m, 3 V standard-cell library.

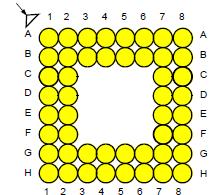

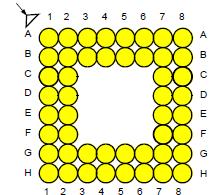

` 48-ball TFSBGAC. (Lead-free package also available.

(See Ordering Information on page 51.)

` Evaluation kit available.Application· Suitable for peripherals with embedded microprocessors.

· Glueless interface to microprocessor buses.

· Support of multifunction USB implementations, such as printer/scanner and integrated multimedia applications.

· Suitable for a broad range of device class peripherals in the USB standard. Pinout Specifications

SpecificationsStresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of this data sheet. Exposure to absolute maximum ratings for extended eriods can adversely affect device reliability.

Absolute Maximum Ratings

| Parameter |

Symbol |

Min |

Max |

Unit |

| Ambient Operating Temperature Range |

TA |

-20 |

85 |

|

| Storage Temperature |

Tstg |

-40 |

125 |

|

| Power Supply Voltage with Respect to Ground |

VDD |

- |

4.2 |

V |

Absolute Maximum Voltage Ratings (0 TA 85)

| Parameter |

Symbol |

Min |

Max |

Unit |

| Voltage on Any Non-USB Pin with Respect to Ground |

- |

VSS-0.3 |

5.5 |

V |

Absolute Maximum Voltage Ratings (20 TA 0)

| Parameter |

Symbol |

Min |

Max |

Unit |

| Persistent* Voltage on Any Non-USB Pin with Respect to Ground |

- |

VSS-0.3 |

3.6 |

V |

| Non-persistent* Voltage on Any Non-USB Pin with Respect to Ground |

- |

VSS-0.3 |

5.5 |

V |

* A persistent voltage level is considered to be one which lasts for more than 25 ns.DescriptionUSS-820FD is a USB device controller that provides a programmable bridge between the USB and a local microprocessor bus. It is available in a 48-ball TFSBGAC package. The USS-820FD allows PC peripherals to upgrade to USB connectivity without major redesign effort. It is programmable through a simple read/write register interface that is compatible with industry-standard USB microcontrollers.

USS-820FD is designed in 100% compliance with the USB industry standard, allowing device-side USB products to be reliably installed using low-cost, off-the-shelf cables and connectors.

The USS-820FD supports 12 Mbits/s full-speed operation. FIFO options support all four transfer types: control, interrupt, bulk, and isochronous, as described in Universal Serial Bus Specification Revision 1.1, with a wide range of packet sizes. Its double sets of FIFO enable the dual-packet mode feature. The dual-packet mode feature reduces latency by allowing simultaneous transfers on the host and microprocessor sides of a given unidirectional endpoint.

The USS-820FD supports a maximum of eight bidirectional endpoints with 16 FIFOs (eight for transmit and eight for receive) associated with them. The FIFOs are on-chip, and sizes are programmable up to a total of 1120 logical bytes. When the dual-packet mode feature is enabled, the device uses a maximum of 2240 bytes of physical storage. This additional physical FIFO storage is managed by the device hardware and is transparent to the user.

The USS-820FD are 8 bytes, 16 bytes, 32 bytes, and 64 bytes for nonisochronous pipes, and 64 bytes, 256 bytes, 512 bytes, and 1024 bytes for isochronous pipes. The FIFO size of a given endpoint defines the upper limit to maximum packet size that the hardware can support for that endpoint. This flexibility covers a wide range of data rates, data types, and combinations of applications.

The USS-820FD can be clocked either by connecting a 12 MHz crystal to the XTAL1 and XTAL2 pins, or by using a 12 MHz external oscillator. The internal 12 MHz clock period, which is a function of either of these clock sources, is referred to as the device clock period (tCLK) throughout this data sheet.

Serial Interface Engine The SIE is the USB protocol interpreter. It serves as a communicator between the USS-820FD and the host through the USB lines.

The USS-820FD functions include the following:

` Package protocol sequencing.

` SOP (start of packet), EOP (end of packet), RESUME, and RESET signal detection and generation.

` NRZI data encoding/decoding and bit stuffing.

` CRC generation and checking for token and data.

` Serial-to-parallel and parallel-to-serial data conversion.

Protocol Layer The protocol layer manages the interface between the SIE and FIFO control blocks. It passes all USB OUT and SETUP packets through to the appropriate FIFO. It is the responsibility of firmware to correctly interpret and execute each USB SETUP command (as documented in the Firmware Responsibilities for USB SETUP Commands section) via the register interface. The protocol layer tracks the setup, data, and status stages of control transfers.

FIFO Control

USS-820FD's FIFO control manager handles the data flow between the FIFOs and the device controller's protocol layer. It handles flow control and error handling/ fault recovery to monitor transaction status and to relay control events via interrupt vectors.

FIFO Programmability

Table 1 shows the programmable FIFO sizes. The size of the FIFO determines the maximum packet size that the hardware can support for a given endpoint. An endpoint is only allocated space in the shared FIFO storage if its RXEPEN/TXEPEN bit = 1. If the endpoint is disabled (RXEPEN/TXEPEN = 0), it is allocated 0 bytes. Register changes that affect the allocation of the shared FIFO storage among endpoints must not be made while there is valid data present in any of the enabled endpoints' FIFOs. Any such changes will render all FIFO contents undefined. Register bits that affect the FIFO allocation are the endpoint enable bits (the TXEPEN and RXEPEN bits of EPCON), the size bits of an enabled endpoint (FFSZ bits of TXCON and RXCON), the isochronous bit of an enabled endpoint (TXISO bit of TXCON and RXISO bit of RXCON), and the FEAT bit of the MCSR register.

If the MCSR.FEAT register bit is set to 1, additional FIFO sizes are enabled for nonisochronous endpoints, as shown in Table 1.

Each FIFO can be programmed independently via the TXCON and RXCON registers, but the total logical size of the enabled endpoints (TX FIFOs + RX FIFOs) must not exceed 1120 bytes. The 1120-byte total allows a configuration with a full-sized, 1024-byte isochronous endpoint, a minimum-sized, 64-byte isochronous feedback endpoint, and the required, bidirectional, 16-byte control endpoint. When the dual-packet mode feature is enabled, the device uses a maximum of 2240 bytes of physical storage. This additional physical FIFO storage is managed by the device hardware and is transparent to the user.

FIFO Access

The transmit and receive FIFOs are accessed by the application through the register interface (see Tables 23-26 for transmit FIFO registers and Tables 27-30 for receive FIFO registers).

The transmit FIFO is written to via the TXDAT register, and the receive FIFO is read via the RXDAT register. The particular transmit/receive FIFO is specified by the EPINDEX register. Each FIFO is accessed serially, each RXDAT read increments the receive FIFO read pointer by 1, and each TXDAT write increments the transmit FIFO write pointer by 1.

Each FIFO consists of two data sets to provide the capability for simultaneous read/write access. Control of these pairs of data sets is managed by the hardware, invisible to the application, although the application must be aware of the implications. The receive FIFO read access is advanced to the next data set by firmware setting the RXFFRC bit of RXCON. This bit clears itself after the advance is complete. The transmit FIFO write access is advanced to the next data set by firmware writing the byte count to the TXCNTH/L registers.

The USB access to the receive and transmit FIFOs is managed by the hardware, although the control of the nonisochronous data sets can be overridden by the ARM and ATM bits of RXCON and TXCON, respectively. A successful USB transaction causes FIFO access to be advanced to the next data set. A failed USB transaction (e.g., for receive operations, FIFO overrun, data time-out, CRC error, bit stuff error; for transmit operations, FIFO underrun, no ACK from host) causes the FIFO read/write pointer to be reversed to the beginning of the data set to allow transmission retry for nonisochronous transfers.

The transmit FIFOs are circulating data buffers that have the following features:

` Support up to two separate data sets of variable sizes (dual-packet mode).

` Include byte counter register for storing the number of bytes in the data sets.

` Protect against overwriting data in a full FIFO.

` Can retransmit the current data set.

All transmit FIFOs use the same architecture (see Figure 2). The transmit FIFO and its associated logic can manage up to two data sets: data set 0 (ds0) and data set 1 (ds1). Since two data sets can be used in the FIFO, backto- back transmissions are supported. Dual-packet mode for transmit FIFOs is enabled by default. Single-packet mode can be enforced by firmware convention (see TXFIF register bits).

The CPU writes to the FIFO location that is specified by the write pointer. After a write, the write pointer automatically increments by 1. The read marker points to the first byte of data written to a data set, and the read pointer points to the next FIFO location to be read by the USB interface. After a read, the read pointer automatically increments by 1.

When a good transmission is completed, the read marker can be advanced to the position of the read pointer to set up for reading the next data set. When a bad transmission is completed, the read pointer can be reversed to the position of the read marker to enable the function interface to reread the last data set for retransmission. The read marker advance and read pointer reversal can be achieved two ways: explicitly by firmware or automatically by hardware, as indicated by bits in the transmit FIFO control register (TXCON).

Receive FIFO

The receive FIFOs are circulating data buffers that have the following features:

` Support up to two separate data sets of variable sizes (dual-packet mode).

` Include byte count register that accesses the number of bytes in data sets.

` Include flags to signal a full FIFO and an empty FIFO.

` Can reread the last data set.

Figure 3 shows a receive FIFO. A receive FIFO and its associated logic can manage up to two data sets: data set 0 (ds0) and data set 1 (ds1). Since two data sets can be used in the FIFO, back-to-back transmissions are supported. Single-packet mode is established by default after a USS-820FD device reset, which sets the RXSPM register bit. Firmware can enable dual-packet mode by clearing the RXSPM bit to 0.

The receive FIFO is symmetrical to the transmit FIFO in many ways. The SIE writes to the FIFO location specified by the write pointer. After a write, the write pointer automatically increments by 1. The write marker points to the first byte of data written to a data set, and the read pointer points to the next FIFO location to be read by the CPU. After a read, the read pointer automatically increments by 1.

When a good reception is completed, the write marker can be advanced to the position of the write pointer to set up for writing the next data set. When a bad transmission is completed, the write pointer can be reversed to the position

of the write marker to enable the SIE to rewrite the last data set after receiving the data again. The writemarker advance and write pointer reversal can be achieved two ways: explicitly by firmware or automatically by hardware, as specified by bits in the receive FIFO control register (RXCON).

The CPU should not read data from the receive FIFO before all bytes are received and successfully acknowledged because the reception may be bad.

To avoid overwriting data in the receive FIFO, the SIE monitors the FIFO full flag (RXFULL bit in RXFLG). To avoid reading a byte when the FIFO is empty, the CPU can monitor the FIFO empty flag (RXEMP bit in RXFLG).

The CPU must not change the value of the EPINDEX register during the process of reading a data set from a particular

receive FIFO. Once the CPU has read the first byte of a data set, the processor must ensure that the EPINDEX register setting remains unchanged until after the last byte is read from that data set. Registers other than EPINDEX may be read or written during this period, except for registers which affect the overall FIFO configuration, as described in the FIFO Programmability section. If EPINDEX is allowed to change during a data set read, incorrect data will be returned by the USS-820FD when subsequent bytes are read from the partially read data set. There is no such restriction when writing FIFOs.

USS-820FD Data Sheet

USS-820FD Data Sheet