Digital Circuit

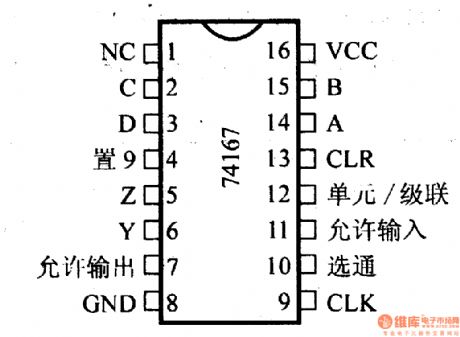

74 Series digital circuit of 74167 BCD synchronization coefficient multiplier

Published:2011/7/29 1:14:00 Author:Lucas | Keyword: 74 Series, digital circuit, BCD , synchronization coefficient multiplier | From:SeekIC

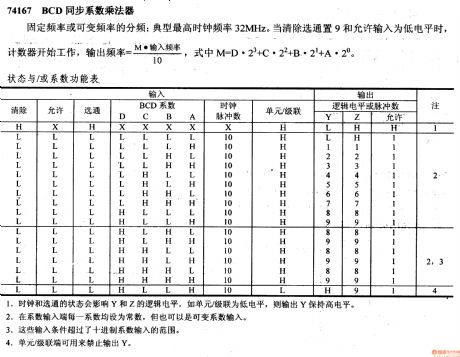

The fractional frequency has the fixed frequency or variable frequency; the typical maximum clock frequency is 32MHz. When the clear strobe sets to 9 and it allows the input to be low, the counter starts to work. 1. The status of clock and strobe has the effect on the logic level Y and Z, for example, unit/ cascade is low, the output Y remains high. 2. Each factor of the factor inputs is set to constant, but also can be a variable factor input. 3. The input conditions have been greater than the decimal input range. 4. Unit/cascade can be used to disable the output terminal Y.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/Digital_Circuit/74_Series_digital_circuit_of_74167_BCD_synchronization_coefficient_multiplier.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: