Position: Home > Circuit Diagram > Basic Circuit > Digital Circuit > 74 Series digital circuit of 74276 four JK flip-flop

Digital Circuit

74 Series digital circuit of 74276 four JK flip-flop

Published:2011/7/29 1:47:00 Author:Lucas | Keyword: 74 Series , digital circuit, four JK flip-flop | From:SeekIC

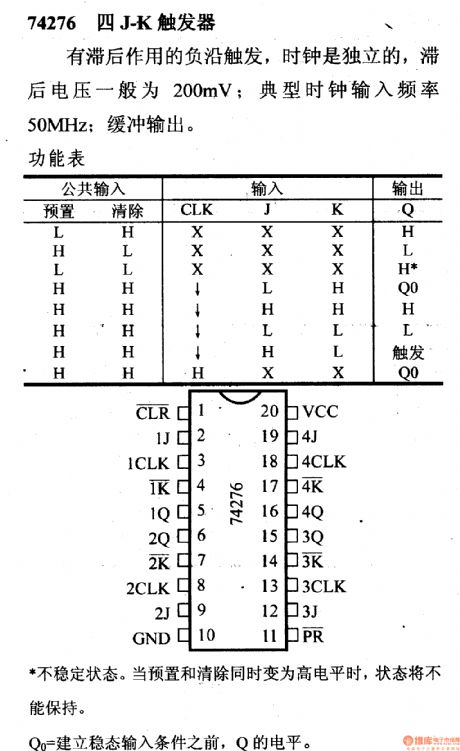

It has the negative edge trigger with lag effect, and the clock is independent, then the hysteresis is typically 200mv; typical clock input frequency is 50MHz; it has buffer output.Unsteady state. When the preset and clear goes high at the same time, the state will not be maintained.

Q0 = the output level of Q before establishing the steady-state input conditions.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Basic_Circuit/Digital_Circuit/74_Series_digital_circuit_of_74276_four_JK_flip_flop.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: