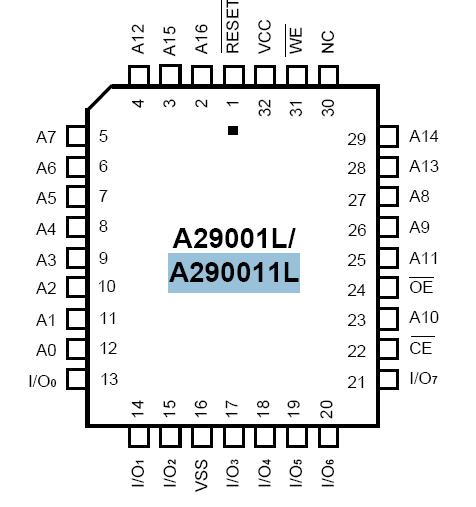

A290011L: Features: ` 5.0V ± 10% for read and write operations` Access times:- 55/70/90 (max.)` Current:- 20 mA typical active read current- 30 mA typical program/erase current- 1 A typical CMOS standby` ...

floor Price/Ceiling Price

- Part Number:

- A290011L

- Supply Ability:

- 5000

Price Break

- Qty

- 1~5000

- Unit Price

- Negotiable

- Processing time

- 15 Days

SeekIC Buyer Protection PLUS - newly updated for 2013!

- Escrow Protection.

- Guaranteed refunds.

- Secure payments.

- Learn more >>

Month Sales

268 Transactions

Payment Methods

All payment methods are secure and covered by SeekIC Buyer Protection PLUS.

A290011L Data Sheet

A290011L Data Sheet