Features: ·Based on ITU Q.933 Annex A and T1.617 Annex D Standards for Frame Relay Service and Additional Pocedures for Permanent Virtual Circuits(PVCs).

·Optional Transparent Mode (no LMI Protocol Processing - all frame data received).

·Local Management Link Protocol with optional Bi-directional message processing.

·Detects and indicates service-affecting errors in the timing or content of events.

·Programmable Timers/Counters: nT1/T391, nT2/T392, nN1/N391, nN2/N392, nN3/N393 and dN1 for the LMI/LIV channel.

·Provides Error Counters for the LMI channel and Congestion Statistics for all the active channels.

·LMI/LIV Frames can be transmitted/received on DLCI 0 or 1023.

·Supports reception of up to 4 octets of address field with a maximum of 8192 active channels or DLCIs (Data Link Connection Identifiers)

·Priority DLCI scheme for channels requiring higher rate of service.

·Buffer Management includes: - Initialization Block - Address Look Up Table

·- Context Table - Separate Receive and Transmit Rings of variable size for each active channel

·On chip DMA control with programmable burst length.

·Handles all HDLC frame formatting: - Zero bit insertion and deletion - FCS (CRC) generation and detection - Frame delimiting with flags

·Programmable minimum frame spacing on transmission (1-62 flags between frames).

·Selectable FCS (CRC) of 16 or 32 bits.

·Testing Facilities: Internal Loopback, Silent Loopback, Clockless Loopback, and Self Test.

·System clock rates up to 25 MHz.

·CMOS process; Fully compatible with both 8 and 16 bit systems; All inputs and outputs are TTL compatible.

·Programmable for full or half duplex operation.

·Pin-for-pin compatible and architecturally the same as the MK50H25 (X.25/LAPD) and MK50H27 (CCS#7).

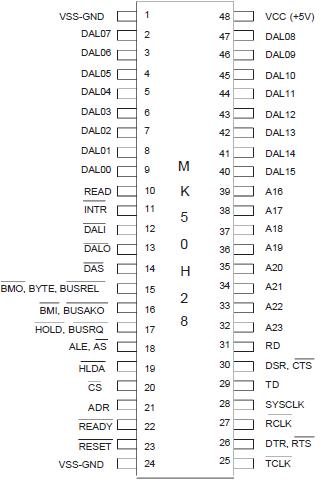

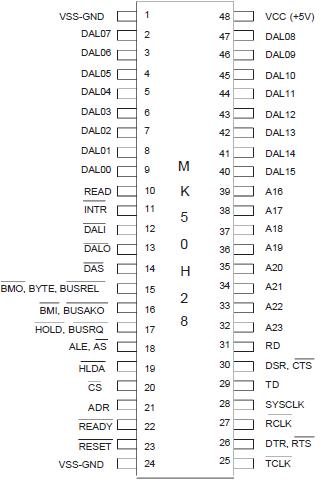

Pinout Specifications

Specifications

|

Symbol |

Parameter |

Value |

Unit |

|

TUB |

Temperature Under Bias |

-25 to +100 |

|

|

TSTG |

Storage Temperature |

-65 to +150 |

|

|

VG |

Voltage on any pin with respect to ground |

-0.5 to VCC+0.5 |

V |

|

PTOT |

Power Dissipation |

0.5 |

W |

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the above device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure

DescriptionThe STMicroelectronics MK50H28 Multi-Logical Link Communications Controller is a CMOS VLSI device which provides link level data communications control for Frame Relay Applications on Permanent Virtual Circuits (PVCs). The MK50H28 will perform frame formating including: frame delimiting with flags, transparency (so-called "bitstuffing"), plus FCS (CRC) generation and detection. It also supports Local Management Interface (LMI) protocol with the "Optional Bidirectional Procedures" (Annex D, T1.617 - 1991 and T1.617a- 1994).

One of the outstanding features of the MK50H28 is its buffer management which includes on-chip dual channel DMA. This feature allows users to receive and transmit multiple data frames at a time. (A conventional serial communications control chip plus a separate DMA chip would handle data for only a single block at a time.) The MK50H28 will move multiple blocks of receive and transmit data directly into and out of memory through the Host's bus. Moreover, the memory management capability includes the chaining of long frames. A possible system configuration for the MK50H28 is shown in Figure 1.

The MK50H28 may be used with any of several popular 16 and 8 bit microprocessors, such as 68000, 6800, Z8000, Z80, LSI- 11, 8086, 8088, 8080, etc.

The MK50H28 may be operated in either full or half duplex mode. In half duplex mode, the RTS and CTS modem control pins are provided. In full duplex mode, these pins become user programmable I/O pins. All signal pins on the MK50H28 are TTL compatible. This has the advantage of making the MK50H28 independent of the physical interface. As shown in Figure 1, line drivers and receivers are used for electrical connection to the physical layer.

MK50H28 Data Sheet

MK50H28 Data Sheet