Features: ` Fully supports provisions of IEEE 13941995 Standard for high performance serial bus and the P1394a2000 Standard1

` Fully interoperable with Firewire(TM) and i.LINK(TM) implementations of the IEEE 1394 Standard.2

` Full P1394a support includes:

Connection debounce

Arbitrated short reset

Multispeed concatenation

Arbitration acceleration

Fly-by concatenation

Port disable/suspend/resume

` Provides one 1394a fully-compliant cable port at 100/200/400 Mbps. Can be used as a one port PHY without the use of any extra external components

` Fully compliant with Open HCI requirements

` Power down features to conserve energy in battery-powered applications include:

Automatic device power down during suspend

Device power down terminal

Link interface disable via LPS

Inactive ports powered-down

` Logic performs system initialization and arbitration functions

` Encode and decode functions included for data-strobe bit level encoding

` Incoming data resynchronized to local clock

` Single 3.3 volt supply operation

` Minimum VDD of 2.7 V for end-of-wire power-consuming devices *While unpowered and connected to the bus, will not drive TPBIAS on a connected port, even if receiving incoming bias voltage on that port

` Supports extended bias-handshake time for enhanced interoperability with camcorders Interface to link-layer controller supports both low-cost bus-holder

` isolation and optional Annex J electrical isolation

` Data interface to link-layer controller through 2/4/8 parallel lines at 49.152 MHz

` Low-cost 24.576 MHz crystal provides transmit, receive data at 100/200/400 Mbps, and link-layer controller clock at 49.152 MHz

` Does not require external filter capacitors for PLL

` Interoperable with link-layer controllers using 3.3 V and 5 V supplies

` Interoperable with other Physical Layers (PHYs) using 3.3 V and 5 V supplies

` Node power class information signaling for system power management

` Register bits give software control of contender bit, power class bits, link active bit, and 1394a features

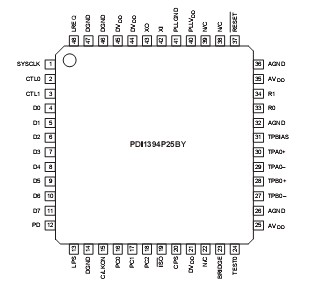

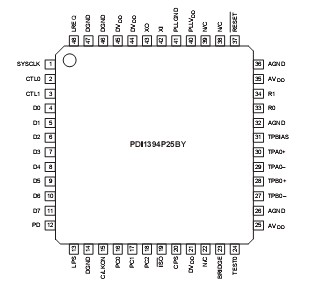

Pinout Specifications

Specifications

|

SYMBOL |

PARAMETER |

CONDITION |

LIMITS |

UNIT |

|

MIN |

MAX |

|

VDD |

DC supply voltage |

|

0.5 |

4.0 |

V |

|

VI |

DC input voltage |

|

0.5 |

VDD +0.5 |

V |

|

VI5V |

5 volt tolerant input voltage range |

|

0.5 |

5.5 |

V |

|

VO |

DC output voltage range at any output |

|

0.5 |

VDD +0.5 |

V |

|

|

Electrostatic discharge |

Human Body Model |

|

2 |

kV |

|

Machine Model |

|

200 |

V |

|

Tamb |

Operating free-air temperature range |

|

0 |

+70 |

|

|

Tstg |

Storage temperature range |

|

65 |

+150 |

|

NOTE:

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

DescriptionThe PDI1394P25BY provides the digital and analog transceiver functions needed to implement a one port node in a cable-based IEEE 13941995 and/or 1394a network. The transceivers include circuitry to monitor the line conditions as needed for initialization and arbitration, and for packet reception and transmission. The PDI1394P25BY is designed to interface with a Link Layer Controller (LLC), such as the PDI1394L40 or PDI1394L41.

PDI1394P25BY Data Sheet

PDI1394P25BY Data Sheet