Features: ` Input data fully compliant with the Transport Stream (TS) definition of the MPEG-2 systems specification (International Standard; November 1994)

` Input data signals: Forward Error Correction (FEC) or descrambler interface

modem data input bus (8-bit wide) PKTDAT7 to PKTDAT0

valid input data indicator (PKTDATV)

erroneous packet indicator (PKTBAD/PKTBAD)

first packet byte indicator (PKTSYNC)

byte strobe signal [for the asynchronous mode only (PKTBCLK)]

` The interface can be configured to either of two modes:

asynchronous mode; PKTBCLK < 9 MHz, for connection to a modem (e.g. FEC)

synchronous mode; PKTBCLK is not used for connection to an external descrambler operating at 9 MHz. The descrambler chip clock (9 MHz; 33% duty cycle) is generated and output to the demultiplexer.

The descrambler chip clock [DCLK (9 MHz, 33% duty

cycle)] is generated and output by the demultiplexer

` External memory; standard 32K * 8-bit static RAM. Required typical access time 50 ns, write pulse width (tWP) 35 ns.

` Effective bit rate: fbit 72 MHz

` Control Interface; 8-bit multiplexed data/address (MDAT7 to MDAT0), memory mapped I/O (P90CE201 microcontroller parallel bus compatible), in combination with two microcontroller interrupt signals (IRQ and NMI). In addition, a number of address input pins (MA9 to MA2) allow direct access to a selected set of demultiplexer registers.

` Output ports: Video; two alternative applications;

third party video decoder compatible (master or slave horizontal or vertical sync generation)

Philips SAA7201 compatible (via general purpose output)

Audio; third party audio decoder, or Philips SAA2500 compatible

Audio/video; third party combined A/V decoder compatible, (programmable)

Teletext; a Teletext Clock/Teletext Data (TTC/TTD) based serial interface to selected teletext decoders (e.g. SAA9042). Alternatively, this interface can be programmed to provide data for Vertical Blanking Interval (VBI) insertion of teletext data. The interface therefore includes a teletext data request input (TTR). In this mode, the interface is compatible with the SAA7183 (EURO-DENC) TXT interface.

HS Data; high-speed data output, outputting entire transport packets, packet payloads, PES packet payloads, or sections (programmable) at byte clock frequency (9 MHz). In the test mode it is capable of outputting copies of either video, audio or other data streams (programmable).

HS pins are combined with the general purpose interface. The general purpose interface is bidirectional, and can therefore, be used as an alternative transport stream input.

` Descrambler; 8-bit wide data input interface, combined with the modem input bus. A descrambler device may output a descrambled transport stream at 9 MByte/s. A 9 MHz descrambler clock is generated and output by the demultiplexer.

` Microcontroller support; only for control, no specific demultiplexing tasks are performed by the microcontroller. However, parsing and processing of Program Specific Information (PSI), and Service Information (SI) is left to the microcontroller.

` Error handling; stream dependent error handling algorithms, invoked either if the PKTBAD/PKTBAD input signal is set, or if the transport_error_indicator bit (MPEG-2 syntax) is set or if the parser detects an MPEG-2 syntax error. Different handling algorithms are applied for the various output ports.

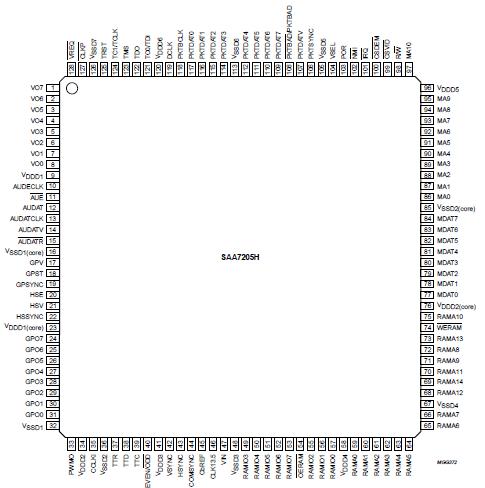

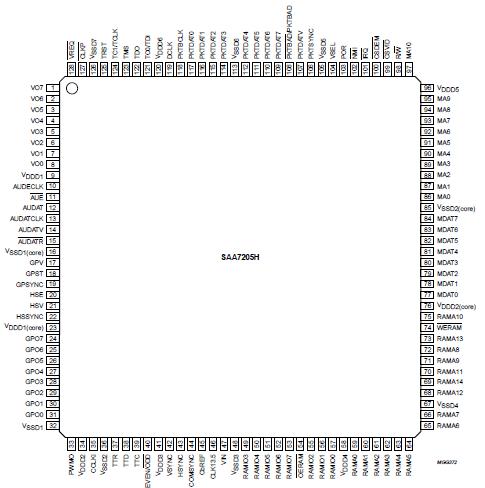

Pinout Specifications

Specifications

| SYMBOL |

PARAMETER |

MIN. |

MAX. |

UNIT |

| VDDD(core) |

digital supply voltage for core |

-0.5 |

+5.0 |

V |

| VDDD(pads) |

digital supply voltage for pads |

-0.5 |

+6.5 |

V |

| VI |

DC input voltage |

-0.5 |

VDDD + 0.5 |

V |

| VO |

DC output voltage; |

-0.5 |

VDDD + 0.5 |

V |

| Ii(max) |

maximum input current |

-10 |

+10 |

mA |

| Io(max) |

maximum output current |

-20 |

+20 |

mA |

| Tstg |

storage temperature |

-65 |

+150 |

°C |

| Tamb |

operating ambient temperature |

0 |

70 |

°C |

DescriptionThis document specifies the MPEG-2 systems demultiplexer IC, SAA7205H, for use in MPEG-2 based digital TV receivers, possibly incorporating conditional access. Such receivers of SAA7205H are to be implemented in, for instance, a Digital Video Broadcasting (DVB) set-top box, or Integrated Receiver Decoder (IRD). An example of a demultiplexer/descrambler system configuration, containing a channel decoder module, source decoders, a system microcontroller and a conditional access system is shown in Fig.1. The main function of the demultiplexer is to separate relevant data of SAA7205H from an incoming MPEG-2 systems compliant data stream and pass it to both the individual source decoders and to the system microcontroller. To support descrambling, the demultiplexer interfaces with the descrambler part of a conditional access system (optional). The demultiplexer therefore generates a 9 MHz descrambler chip clock.

SAA7205H Data Sheet

SAA7205H Data Sheet