Features: • Two input data formats

- 4:2:2 luminance and chrominance parallel (2 x 8 wires)

- ITU-R 656 data format (8 wires)

• Two different representations of input chrominance data

- 2's complement code

- Positive dual code

• Flexible input sync controller

• Flexible compression of the input signal

- Digital vertical compression of the input signal (1.0, 1.25, 1.5, 1.75, 2.0, 3.0, 4.0)

- Digital horizontal compression of the input signal (1.0, 2.0, 4.0)

• Noise reduction

- Motion adaptive spatial and temporal noise reduction (3D-NR)

- Temporal noise reduction for luminance frame based or field based

- Temporal noise reduction for chrominance field based

- Separate motion detectors for luminance and chrominance

- Flexible programming of the temporal noise reduction parameters

- Automatic measurement of the noise level (5 bit value, readable by I²C bus)

• 3-D motion detection

- High performance motion detector for scan rate conversion

- Global motion detection flag (readable by I²C bus)

- Movie mode and phase detector (readable by I²C bus)

• TV mode detection by counting line numbers (PAL, NTSC, readable by I²C bus)

• Embedded memory

- 5 Mbit embedded DRAM core for field memories

- 192 kbit embedded DRAM core for line memories

• Flexible clock and synchronization concept

- Decoupling of the input and output clock system possible

• Scan rate conversion

- Motion adaptive 100/120 Hz interlaced scan conversion

- Motion adaptive 50/60 Hz progressive scan conversion

- Simple static interlaced and progressive conversion modes

for 100/120 Hz interlaced or 50/60 Hz progressive scan conversion:

e.g. ABAB, AABB, AA*B*B, AAAA, BBBB, AB, AA*

- Simple progressive scan conversion with joint lines:

50 Hz -> 60, 70, 75 Hz progressive

60 Hz -> 70, 75 Hz progressive

- Large area and line flicker reduction

• Flexible digital vertical expansion of the output signal (1.0, ... [1/32] ... , 2.0)

• Flexible output sync controller

- Flexible positioning of the output signal

- Flexible programming of the output sync raster

- External synchronization by backend IC possible (e.g. split screen for one TV channel with joint lines and one PC VGA channel)

• Signal manipulations

- Insertion of coloured background

- Vertical and/or horizontal windowing with four different speed factors

- Flash generation (for supervising applications, motion flag readable by I²C bus)

- Still frame or field

- Support of split screen applications

- Multiple picture display - Tuner scan (4 and 16 times for 4:3, 12 times for 16:9 tubes)

- Support of multi picture display with PIP or front-end processor with integrated scaler (e.g. 9 times display of PIP pictures, picture tracking, random pictures, still-in-moving picture, moving-in-still picture)

• I²C-bus control (400 kHz)

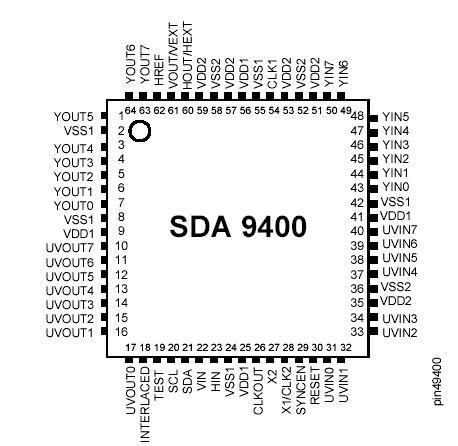

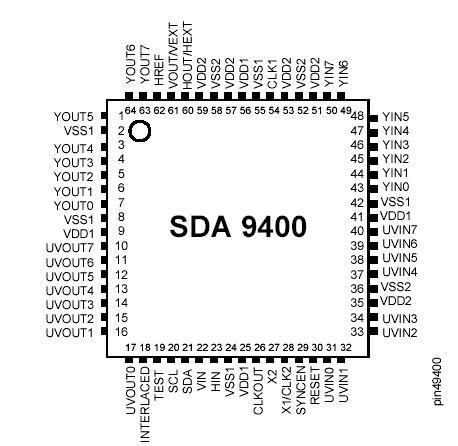

• P-MQFP-64 package

• 3.3 V ± 5% supply voltage

Pinout Specifications

Specifications

| Parameter |

Symbol |

Min |

Max |

Unit |

Remark |

| Operating Temperature |

TA |

0 |

70 |

°C |

|

| Storage temperature |

Tstg |

-65 |

125 |

°C |

|

| Junction temperature |

Tj |

|

125 |

°C |

|

| Soldering temperature |

TS |

|

260 |

°C |

|

| Soldering time |

ts |

|

10 |

s |

|

| Input voltage |

VI |

-0.3 |

VDD+0.3 |

V |

not valid for I²C bus pins |

| Output voltage |

VO |

-0.3 |

VDD+0.3 |

V |

not valid for I²C bus pins |

| Input Voltage |

VI |

-0.3 |

5.5 |

V |

I²C bus pins only |

| Output Voltage |

VO |

-0.3 |

5.5 |

V |

I²C bus pins only |

| Supply voltages |

VDD |

-0.3 |

3.8 |

V |

|

| Total Power Dissipation |

THD |

|

1 |

W |

|

| ESD Protection |

ESD |

-2.0 |

2,0 |

kV |

MIL STD 883C method

3015.6, 100pF, 1500(HBM) |

ESD

protection |

ESD |

-1.5 |

1,5 |

kV |

EOS/ESD Assn. Standard

DS 5.3-1993 (CDM) |

Latch-up

protection |

|

100 |

100 |

mA |

all inputs/outputs |

DescriptionThe SDA 9400 is a new component of the Micronas MEGAVISION® IC set in a 0.35 µm embedded DRAM technology (frame memory embedded). The SDA 9400 is pin compatible to the SDA 9401 (field memory embedded). The SDA 9400 comprises all main functionalities of a digital featurebox in one monolithic IC.

The scan rate conversion to 100/120 Hz interlaced (50/60 Hz progressive)SDA 9400 is based on a motion adaptive algorithm. The scan rate converted picture can be vertically expanded. The SDA 9400 has a freerunning mode, therefore features of SDA 9400 like scan rate conversion to e.g. 70, 75 Hz with joint lines or multiple picture display (e.g. tuner scan) are possible.

Due to the frame based signal processing, the noise reduction of SDA 9400 has been greatly improved. Furthermore separate motion detectors for luminance and chrominance have been implemented. For automatic controlling of the noise reduction parameters a noise measurement algorithm is included, which measures the noise level in the picture or in the blanking period. In addition a spatial noise reduction is implemented, which reduces the noise even in the case of motion. The input signal of SDA 9400 can be compressed horizontally and vertically with a certain number of factors. Therefore split screen is supported.

Beside these additional functions of SDA 9400 like coloured background, windowing and flashing are implemented.

SDA9400 Data Sheet

SDA9400 Data Sheet