A/D converter

COMPRESSING_A_D_CONVERSION

Published:2009/6/30 1:50:00 Author:May | From:SeekIC

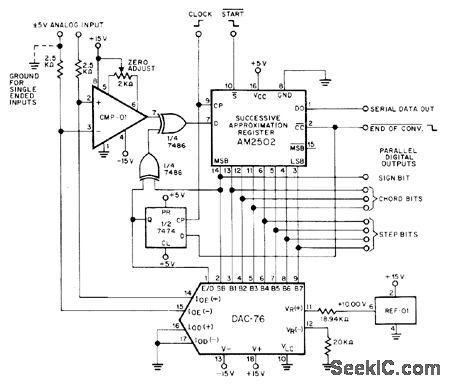

Step size increases as output changes from zero scale to full scale, in contrast to conventional linear converter in which step size is constant percentage of full scale. Uses Precision MonolithIcs DAC-76 D/A converter in combination with CMP-01 comparator, any standard EXCLUSIVE-OR gate, and successive-approximation register for conversion logic. Encoding sequence begins with sign-bit comparison and decision. Bits are con verted with successive-removal technique, starting with decision at code 011 1111 and turning off bits sequentially until all decisions have been made. Conversion is completed in nine clock cycles.— COMDAC Companding D/A Converter, Precision MonolithIcs, Santa Clara, CA, 1977, DAC-76, p 12.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/A-D_D-A_Converter_Circuit/A-D_converter/COMPRESSING_A_D_CONVERSION.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

Code: