© 2008-2012 SeekIC.com Corp.All Rights Reserved.

Measuring and Test Circuit

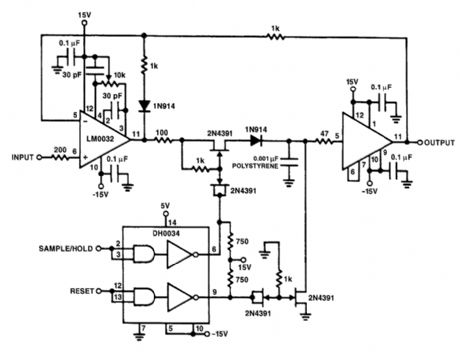

HIGH_SPEED_PEAK_DETECTOR_WITH_HOLD_AND_RESET_CONTROLS

Published:2009/6/18 3:08:00 Author:May | From:SeekIC

The LH0033 and LH0063 are useful in high-speed sample-and-hold or peak detector circuits be-cause of their very high speed and low-bias-current FET input stages. The high-speed peak detector circuit shown could be changed to a sample-and-hold circuit simply by removing the detector diode and reset circuitry. For best accuracy, the circuit can be trimmed with the 10-kΩ offset adjustment pot shown. The circuit has a typical acquisition time of 900 ns, to 0.1% of the final value for the 10-V input step signal, and a droop rate of 100 μV/ms, Even faster acquisition time can be achieved by re-ducing the hold capacitor value.

Reprinted Url Of This Article:

http://www.seekic.com/circuit_diagram/Measuring_and_Test_Circuit/HIGH_SPEED_PEAK_DETECTOR_WITH_HOLD_AND_RESET_CONTROLS.html

Print this Page | Comments | Reading(3)

Article Categories

power supply circuit

Amplifier Circuit

Basic Circuit

LED and Light Circuit

Sensor Circuit

Signal Processing

Electrical Equipment Circuit

Control Circuit

Remote Control Circuit

A/D-D/A Converter Circuit

Audio Circuit

Measuring and Test Circuit

Communication Circuit

Computer-Related Circuit

555 Circuit

Automotive Circuit

Repairing Circuit

New published articles

Response in 12 hours

Code: